在数字通信中,误码率BER(Bit Error Rate)是衡量通信系统质量的一项重要指标。无论是设备故障、传播衰落、码间干扰、临近信道干扰等因素都可能造成系统性能恶化甚至造成通信中断,其结果都可通过误码的形式表现出来[1]。因此,误码测试仪是现代通信系统的主要测试仪器之一。

目前,通常使用的传统误码测试仪虽然具有测试内容丰富、测试结果直观等优点,但是由于通信系统复杂程度的不断增加,接口形式变化多样以及一些非标准码率的应用,使得传统误码测试仪的使用受到了一定的限制。另一方面,近年来FPGA技术得到了迅速发展,使用FPGA设计电路具有很大的灵活性,可以大大提高集成度和设计速度,还可以简化接口和控制,有利于提高系统的整体性能和工作可靠性。本文即介绍了一种基于FPGA的RS485接口误码测试仪的设计和实现。该设计具有系统简单、功能可靠、接口独特等特点,并且增加了传统误码测试仪所没有的测量系统传输延时的功能。

1 设计背景

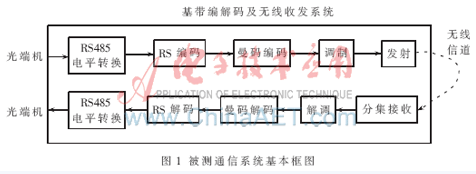

本文所设计的误码测试仪主要用于测试某通信系统的误码性能。该通信系统是一个庞大复杂的系统,本文主要介绍信道部分,包括基带的信道编解码和无线信道的收发,其基本框图如图1所示。

为了在线路传输上保证良好的抗干扰能力,系统采用了RS485接口,选用了4.096 Mb/s的码率。因此,为了测试图1所示系统的误码性能,误码测试仪必须具有以下指标:

(1) 逻辑接口:RS485差分信号。

(2) 物理接口:DB9。

(3) 码率:4.096 Mb/s。

传统误码测试仪通常都不具备以上3项指标,本文设计的误码测试仪满足了上述3项指标。

2 误码测试原理

构成误码测试仪的方案有多种形式,其基本工作过程可以概括为以下几个步骤:

(1) 以某种方式产生和发送码组相同的码形,以相同相位的本地码组作为比较标准。

(2) 将本地码组与接收码组逐个进行比较,并输出误码脉冲信号。

(3) 对误码脉冲信号进行统计,并给出相应的误码率。

在通信工程应用中,为了最大程度地模拟真实通信中的数据流的统计特性,通常采用二进制伪随机序列。对于伪随机序列有以下几点要求[2]:

(1) 应具有良好的伪随机性,即应具有和随机序列类似的随机性。

(2) 应具有良好的自相关、互相关和部分相关特性,即要求自相关峰值尖锐,而互相关和部分相关值接近于零。这是为了接收端的准确检测,以减小差错。

(3) 要求随机序列的数目足够多,以保证在码分多址的通信系统中,有足够多的地址提供给不同的用户。

根据本地码组发生器的构成方式不同,误码测试仪可分为多种类型,本文采用的是逐位检测式,其使用的码组为最大长度线形移位反馈寄存器序列,即m序列。其工作原理为:本地的m序列发生器产生的m序列和所接收的m序列进行逐位比较,若两个m序列同步,则比较器输出的是传输误码;若两个m序列不同步,则比较器输出的是由失步造成的误码。由于失步造成的误码较大(根据m序列的特性,其误码率应为0.5),因此可根据误码率门限来区分检测系统是否失步。若失步,则让本地m序列发生器等待一个时钟周期,再依次逐位比较,并逐位控制本地m序列发生器的等待时间,直到两序列完全同步为止。

3 硬件设计

本系统用单片机作为主控芯片,由FPGA完成误码测试的工作,将得到的误码信息传送给单片机,单片机进行误码率的计算后送液晶屏进行显示。m序列的发送和接收都是通过RS485接口进行的。本系统单片机选用的是51系列的STC89LE58RD+,3.3 V供电,可以减小系统功耗。FPGA选用了Xilinx公司的SPARTNANII-E系列的XC2S300E,其内部包括了30万个逻辑门和其他丰富的资源,可以满足本系统的需要。RS485接口芯片选用Analog Device公司的ADM4857,它是一款10 Mb/s码率、全双工的485接口芯片[3-4]。系统的硬件框图如图2所示。

4 软件设计

软件部分是该系统功能实现的核心,主要包括了单片机和FPGA两大部分。

(1) 单片机软件

单片机作为该系统的主控芯片,主要完成FPGA通信控制、误码率计算、液晶显示控制等功能。开机后,单片机控制系统进入挂起状态,等待按下start按钮。开始工作后,单片机每隔1 s向FPGA请求刷新1次误码数据,FPGA则将误码数据通过SPI总线传送给单片机。单片机将取得的误码数据换算成误码率连同得到的系统传输延迟时间一起送到LCD显示。单片机软件的流程图如图3所示。

(2) FPGA逻辑设计[5-6]

本系统大部分功能通过FPGA实现,使用Verilog编写程序。由于采用的是逐位比较式方案,因此,首先由m序列产生模块产生4.096 Mb/s码率的m序列,送入反相器作为源端。反相器是为了人为产生误码而设置的。当按下按键时,反相器使能,将m序列1位反相后输出,即相当于产生了1个误码。m序列和时钟同时输出给被测系统,经被测系统后再返回给误码测试仪。误码测试仪对输入的m序列和本地产生的m序列进行同步,同步以后,在固定寄存器中置入64位m序列数据。在源端,固定寄存器和移位寄存器不断进行比较,直到两者一致,则启动延时计数器,同时接收端移位寄存器与固定寄存器进行比较,当两者一致时关闭计数器,此时计数器中的数值即为被测系统的延时。另一方面,同步以后,开始进行误码统计。若在设置的测试周期内误码率大于设定的门限值,则认为失步,重新开始同步。最后,将误码数和系统延时数通过SPI接口送给单片机,进行误码率和系统延时的计算,将计算结果显示在LCD上。SPI接口是通过软件进行模拟的。整个FPGA内部的模块框图如图4所示。

5 系统设计仿真

对设计完成后的主要功能模块进行了仿真以验证其功能的正确性。

(1) m序列产生器仿真

本设计采用了23级m序列以确保伪随机序列的特性,其本原多项式为f(x)=1+x5+x23,仿真波形如图5所示。

(2) SPI接口仿真

FPGA与单片机之间采用SPI接口进行通信。外围设备接口SPI通常有3~4条信号线,本文采用3线方式,即片选线SS、时钟线SCK和数据线SDIO。SS为低时有效,在SCK的同步下传送数据,仿真波形如图6所示。

(3) 系统仿真

系统开始工作并正确同步后,开始误码和延时的统计。每当单片机发送1个请求数据信号,就送出当前的误码数和延时数,单片机进行计算后送显示器显示。系统仿真波形如图7所示。

6 调试

调试是整个设计实现的关键步骤。经过调试,最终实现了设计的所有功能。下面给出在设计和调试中的一些经验教训以供参考。

(1) 51单片机的Port 1端口默认情况下没有上拉电阻,因此需要特别注意。在调试初期就是因为没有在外部加上拉电阻而导致与FPGA通信不正常。

(2) RS485接口芯片对于差分线的输入输出阻抗匹配要求比较严格,需要根据手册要求选择合适的匹配电阻,否则会导致输入输出差分信号质量严重劣化,影响系统正常工作。

(3) FPGA与单片机通信等功能需要特别注意时序的配合问题,否则可能导致通信不正常。可以通过选择适当的触发沿来调整时序。

本文介绍了一种基于FPGA的RS485接口的误码测试仪的设计原理和实现过程。与传统的误码测试仪相比,本误码测试仪具有原理简单、接口独特、可测试系统延时等特点。此外,由于FPGA良好的可扩展性,可以在不改变硬件电路的基础上方便地增加或修改相应的功能,增加了系统的可扩展性。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网