一种基于CPLD的DSP人机接口模块设计 (1)CPLD(Complex programmable Logic Device,复杂可编程逻辑器件)是在传统的PAL、GAL基础上发展而来的,具有多种工作方式和高集成、高速、高可靠性等明显的特点。

在超高速领域和实时测控方面有非常广泛的应用,日前的CPLD普遍基于E2PROM和Flash电可擦除技术,可实现100次以上擦写循环。

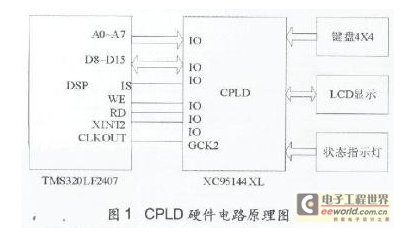

CPLD选择及其扩展模块的设计

由于TMS320LF2407A是3.3v电平供电的,所以CPLD我们也选择3.3v电平供电的XL型号。XC95144XL是Xilinx公司XC9500系列的一种。它的性能指标为;IO口可配置为3.3v或5v操作。所有输出都提供24mA驱动能力;XC295144XL有100个宏单元、3200个可用门和144个寄存器;实现在系统编程,所有器件都支持IEEE1149(JTAG)边界扫描,最小编程/擦除周期为10000次。

其中,DSP(Digital Signal Processor)与CPLD的连接是通过DSP的外部存储器接口实现的。我们通过/IS管脚将其扩展到外部I/O空间,数据总线的高8位和地址总线的低8位与CPLD相连,并且我们将DSP的CLKOUT引脚与CPLD的IO/GCK2连接,为CPLD提供时钟源,由干CLKOUT输出的频率非常高,所以DSP与CPLD的连线应该尽量短,而且要做一些抗干扰的处理,XINT2是DSP的中断引脚,它的作用是当CPLD确定键盘按键的数值后,利用中断将键值传送到DSP中。

CPLD硬件结构设计如图所示:

CPLD的设计主要是利用CPLD对键盘、液晶和各种状态指示灯进行控制。由于TMS320LF2407A的I/O管脚和各种特殊功能是复用的,如果将键盘、LCD显示以及各种状态指示灯直接和DSP相连的话,这将造成它的极大浪费,所以我们在它们中间用CPLD作为桥梁。

另一更为重要的原因是键盘和LCD显示是在一个相对较低的速度下实现的,这对于高速数据处理的DSP来说是无法接受的,我们设计的主要用意是:

对于LCD显示,我们将DSP中的数据发送到CPLD,然后DSP去做其他的事情,而后续显示的任务由CPLD完成,CPLD将在LCD允许的速度下对其进行操作即可达到显示目的。

对于键盘,我们将键盘的各种处理进行完之后通过中断来通知DSP,然后DSP进行取数操作,这样的话并不会影响到整个系统的运行速度。

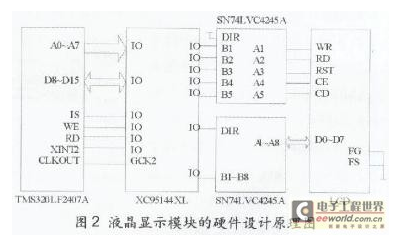

由于LCD具有低功耗、体积小、质量轻、超薄等诸多其他显示器无法比拟的优点,它广泛用干各种智能型仪器和低功耗电子产品中。对于数据采集系统来说,液晶显示模块主要功能是显示系统的采样速率及试样所受的应力值。为了解决快速DSP和慢速外设之问接口的问题,根据上述分析系统采用了以CPLD为桥梁的液晶显示模块。其主要的工作流程是:DSP把显示的数据送给CPLD,然后DSP去做其他的事情,而后续显示的任务将在LCD允许的速度下得到显示。

液晶显示模块选择

数显液晶模块:这是一种由段型液晶显示器件与专用的集成电路组装成一体的功能部什,只能显示数字和一些标识符号。

液晶点阵字符模块:它由点阵字符液晶显示器件和专用的行列驱动器及必要的连接件、结构件装配而成,可以显示数字和西文字符,一般本身具有字符发生器。这种模块的点阵排列是由5×7成5 x 8,5×1的一组像素点阵排列而成的。每组为一位,每位间有一点间隔,每行间也有一点的间隔,所以不能显示图形。

直剪仪数据采集系统的显示特点是不仅能显示模拟拉剪的过程,也要能显示中文、西文操作菜单和各种测量数据,所以以上两种液晶显示模块均不符合本仪器的显示要求。

我们选用的是大连东福的EDM240128F点阵图形LCD。它的最大特点是具有独特的硬件初始值设置功能,显示驱动所需的参数如占空比系数。驱动传输的字节数/行及字符的字体选择等均由引脚电平设置,这样初始化在上电时就已经基本设置完成,软件操作的主要精力就可以全部用于显示画面的设计上了,可以图形方式、文本方式及图形和文本合成方式进行显示,以及文本方式下的特征显示,还可以实现图形拷贝操作。它采用T6963C内核控制器,图2为液晶显示模块硬件设计的原理图。

电平转换芯片的选择

由于CPLD为3.3V的器件,而LCD是5V的器件。所以为了CPLD和LCD之间的电平匹配,需要借助电平转换芯片来完成从3.3V到5V之间的相互转换。选择的电平转换芯片是TI公司的SN74LVC4245A芯片,这个芯片的数据传输方向是双向的,在引脚DIR的作用下,既可以实现从3.3v向5v转换,也可以实现从5v向3.3v转换。

为了液晶模块能够正确的工作,液晶需要上电复位。本设计中采用的字体是8×8点,所以在硬件电路设计时将FS引脚拉低。

在硬件设计时,我们需要注意的问题是:

(1)在VDD对地(Vss)间接0.1u左右电容去耦,接10u或20u电容滤波;

(2)模块的复位脚/RST接一个复位电路,而且我们也将/RST与CPLD相连,这样我们也可以利用DSP对其进行复位,使得可以是液晶进行定时刷新,预防一些其他干扰;

(3)在做实验时,FG(铁框地线、不能悬空,暂时与数字地连接。

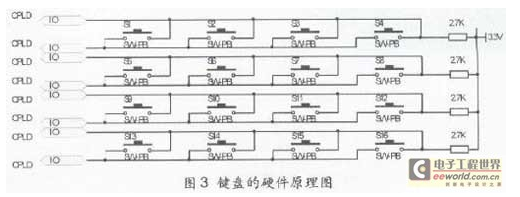

键盘硬件设计

键盘在信号采集系统中是一个很关健的部件,它能向系统输入数据、传送命令等功能,是人工干预系统的主要手段,本系统所用键盘是常用的4×4矩阵式键盘。

16个键盘有0~9数字键,上翻,下翻键,编程键,输入键,擦除键,点号健等。键盘的行线和列线分圳连接CPLD的一个I/O引脚。键盘的行线上有一个2.7k的上拉电阻将行线所连接的CPLD的I/O引脚上拉直高电平。

键盘工作原理

按键设置在行、列线空点上,行、列线分别连接到按键开关的两端。行线通过上拉电阻接到3.3v上。平时无按键动作时,行线处于高电平状态,而当有按键按下时,行线的电平状态将由与此行线相连的列线电平决定。列线电平如果为低,则行线电平亦为低,列线电平如果为高,则行线电平亦为高。这一点是识别矩阵键盘按键是否按下的关键所存。由于矩阵键盘中行、列线为多键共用,各按键均影响该键所在行和列的电平。因此各按键彼此将互相影响,所以必须将行、列线信号配合起来并作适当的处理,才能确定闭合键的位置。

结语

本文简单介绍了TI16位控制器DSP与液晶显示模块及键盘模块之间的接口方案.利用了CPLD来进行逻辑转换和控制。提供了一种高速器件和慢速接口直接的连接方法,通过这个接口方案研究,为以后系统的开发提供了一种新的思路。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网