关于摩尔定律的经济活力问题,有很多的讨论。在过去的一年中,20nm节点进入到这个辩论的前沿和中心。无论说辞如何,包括赛灵思在内的行业领导在20nm研发上的积极推动都没有停止。 只有一个原因可以解释这些行业领导者的积极行动:20nm为创造更高的客户价值提供了巨大的机会,比如赛灵思,它使其客户能够应用到领先其领先竞争对手整整一代的产品系列,而且将为他们提供比以往任何时候都更具吸引力的ASIC和ASSP可编程替代方案。

赛灵思正在打造20nm All Programmable 产品系列,专门满足下一代的、更加“智能”、集成度更高、亟需更高带宽的系统。这些应用包括: 1)智能Nx100G - 400G有线网络;2)高级无线基站部署智能自适应天线、认知技术、基带和回程设备3)高吞吐量、低功耗的数据中心存储、智能网络和高度集成的低时延应用加速;4)图像/视频处理以及面向新一代显示、专业摄像机、工厂、高级汽车驾驶员辅助和监视系统的嵌入式视觉;以及5)面向几乎所有可以想象到的应用的尖端连接技术。

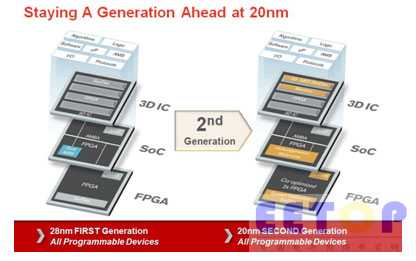

在20nm保持领先一代的地位

为了解20nm所带给赛灵思产品和客户应用的真正价值,首先必须了解其在28nm技术创新上所实现的的超越节点的价值。对赛灵思来说,进入20nm, 并不是传统的简单地迁移到下一个节点,它已经在28nm时代推出了众多的FPGA创新,率先推出了全球行业第一个商用的All Programmable 3D IC和。所有这些已经开始发售的All Programmable 器件,采用了所有形式的可编程技术,远远超出硬件可编程的范畴,实现了软件可编程,超出了数字进入了模拟混合信号(AMS),超出了单芯片发展到了多芯片的3D IC。这种新一代器件所带来的价值现在已经被数百家的客户所证明。

图1:赛灵思正在开发其第二代SoC,3D IC以及下一代FPGA

在20nm,赛灵思目前正在开发其第二代SoC和3D IC技术,以及下一代的FPGA技术。相比于竞争对手,赛灵思拥有多年前率先创新的先发优势。其中包括FPGA性能/瓦的突破,与客户一起更好微调的更成熟的SoC和3D IC技术,与其下一代Vivado设计套件“协同优化”的器件。 赛灵思在系统中重新定义了高性能收发器的设计和优化。 这让赛灵思能够更有效地把20nm的附加价值引入领先的和业经证明的28nm技术之中, 让客户的创新继续 保持领先一代。

从28nm到20nm FPGA进一步优化性能/瓦

28nm 7系列FPGA的创新,把工艺技术上的创新 (与台积电(TSMC)共同开发的高性能低功耗(HPL)技术)与针对最小化静态和动态功耗、最大化主要构建模块性能的众多优化完美结合,让赛灵思能够 提供超越节点的性能/瓦价值优势。与此同时, 赛灵思还能够提供最高的I/O、DDR和收发器带宽,以及针对系统内信道优化的业界最佳的收发器自适应均衡器。

8系列FPGA为赛灵思在20nm继续保持领先一代的地位奠定了基础。这些器件将利用与台积电的28nm HPL工艺性能/瓦特征相似的20nm SoC工艺。将系统级性能提升2倍,内存带宽扩大2倍,总功耗降低50%,逻辑功能集成和关键系统建模加速1.5倍多。设计人员在高性能应用中,可以用到更高的速度架构及第二代专为系统而优化的收发器。而LTE无线、和图像/视频应用的开发人员,可以利用其更快的DSP, BRAM和DDR4内存接口。所有应用都将受益于赛灵思的下一代路由体系结构, 可以轻松地扩展超过90%的资源利用率,实现更高的结果质量及更快的设计收敛。

第一代到第二代All Programmable SoC

赛灵思的28nm Zynq-7000 All Programmable SoC是行业第一个硬件、软件和I/O均可编程的器件。通过实现双核® A9嵌入式系统、DSP、逻辑和主流AMS功能的集成,让赛灵思能够再次为行业提供领先一代的系统性能、集成度和低功耗

为在20nm继续居于领先一代的地位,赛灵思将借助一个新的异构处理系统,有效地提供更高的系统性能。 这个嵌入式系统将被用超过 2倍的互连带宽耦合到下一代FPGA架构中。在芯片上的模拟混合信号性能将翻一番,同时可编程I/O将随着下一代DDR4和PCI Express®接口而升级。这种新级别的嵌入式处理性能和I/O带宽被赋予SoC级的功耗和安全管理。第二代All Programmable SoC将实现最高水平的可编程系统集成,并满足最严格的的系统级规格。

从第一代到第二代All Programmable 3D IC

和一个纯粹的单芯片解决方案所可能达到的结果相比,赛灵思28nm同构和异构Virtex® 3D IC把设计容量、 系统级性能和系统集成的水平均整整翻了一番, 提供了领先一代的价值优势。通过赛灵思堆叠硅片互连技术(SSIT)中的硅中介层,赛灵思 FPGA和收发器混合信号裸片和超过10,000个可编程互连集成在一起。

为在20nm继续领先一代,赛灵思将利用一个两级接口扩大其3D IC的架构,让同构和异构裸片的集成均能基于开放的行业标准实现。从而把逻辑容量扩展1.5倍或增加30-40M ASIC等效门的设计。此外,这些器件将拥有4倍的收发器带宽,利用> 33GB/s的收发器(最终到56GB/s)。 此外, DDR4高性能存储器接口,以及具有更宽更高带宽、更低功耗的集成的存储裸片, 将实现更高性能的应用。

要支持最高的级别、最高的性能和简便的设计, 可编程互联的带宽要增加5倍以上。有了这个新级别的互连和新型可编程芯片和内存的功能,赛灵思正在开发第二代 All Programmable 3D IC技术,致力于实现最高层次的可编程系统集成。

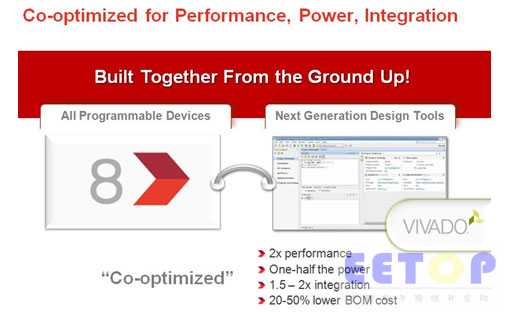

图2:赛灵思利用下一代Vivado设计套件协同优化20nm硅片

针对结果质量和生产力从优化发展到“协同优化”

在领先地位不断扩展至28nm的过去4年中,赛灵思从头全新开发了一个下一代的设计环境与工具套件—Vivado。如果没有这样的设计套件,赛灵思公司的3D IC技术就不能得到有效的利用。对于FPGA和SoC,新的设计套件进一步把设计的结果质量(QOR)提升了高达3个速度等级,削减动态功耗高达50%,布线能力和资源利用率提升20%多,并加快实现速度高达4倍。

目前,赛灵思利用下一代Vivado 设计套件, 进一步“协同优化”其20nm芯片器件。通过构建和优化工具,器件和IP相结合,设计人员可以最大化地释放芯片的价值,同时缩短他们的设计和实现过程。因此,这些新一代20nm的FPGA中,第二代All Programmable SoC和第二代3D IC技术将可以提供领先一个节点的性能优势,大幅降低功耗, 提供业界最高水平的可编程系统集成, 并进一步加速集成和实现的速度。

提供更高的客户价值

半导体行业的领导者正在逐步发现20nm的价值,而且一些设计已经正在进行中。赛灵思公司看到了这个工艺节点所拥有的巨大潜力,因此也在不断地探索新的方式,致力于通过28nm已经建立且在20nm将继续扩展的创新技术持续发掘这些潜在的价值。这些新的产品将提供最引人注目的ASIC和ASSP可编程替代方案。把20nm技术部署在一个All Programmable FPGA和第二代SoC和3D IC技术相结合的产品系列之中, 将使得赛灵思能够提供领先典型工艺节点整整一代的更高价值,同时也使得赛灵思及其客户都能够领先其竞争对手整整一点。 当赛灵思的产品系列正式推出的时候将会宣布每个系列的更多细节。赛灵思在20nm FPGA上正同战略客户开展通力协作,并提供有限制进入的产品定义与技术文档信息。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网