1 引言

随着存储技术的不断进步,Flash Memory的存储容量越来越大,读写数度越来越快。性能价格比越来越高。但是,NAND Flash本身存在缺点,归纳起来有两点:读写控制时序复杂和位交换(o、1反转)问题。NAND Flash器件能够复用指令、地址和数据总线,从而节省了引脚数量,但引脚不仅承担着数据总线的功能,还承担着地址及指令总线的功能,所以造成接口控制时序复杂。位反转的问题更多见于NAND Flash,NAND Flash的供应商建议使用NAND Flash的同时使用EDC/ECC校验算法。

本文实现的NAND Flash控制器放置在CPU和NANF Flash器件之间,实现了NAND Flash的无粘接接口,可以大大简化CPU对NAND Flash的操作时序,提高CPU的使用效率。ECC功能可以保证存储数据的准确性,ECC模块和主控模块相对独立,在不需要ECC功能的时候,只需不使能ECC模块,方便灵活。

2 控制接口电路的功能特性

整个控制接121电路分为两大功能模块:第一个功能模块为主控制器模块,该模块简化NAND Flash的接口时序,可以为NAND Flash设计一个无粘接接口(Glueless Inter一face),从而使得对NAND Flash操作的时序复杂程度大大降低,使得NAND Flash接口映射为一个类似于SRAM的无粘结接口。第二个功能模块是ECC模块,该模块对512个字节能纠正单比特错误和检测双比特错误,但对单比特以上的错误无法纠正。对两比特以E的错误不保证能检测。

两个功能模块相对独立,ECC功能模块位于主控制器模块与NAND Flash芯片之间,可以选择工作与不工作,主控制器模块的所有命令都会通过ECC模块传给NANDFlash芯片。当令ECC模块不工作时。ECC模块就相当于连接主控制器模块与NAND Flash芯片的导线;当ECC模块工作时。只会在丰控制器模块的操作中加入一些步骤,并不会打乱主控制器模块的操作时序。

3 主控制器

3.1寄存器和缓存配置

主控制器的外部接口类似于SRAM的,然而SRAM只有读和写两种主要操作。而NAND Flash除r页编程与读操作之外还有ID读取、重置、块擦除和状态读取等操作,在不改变接口的情况下只能采用与NAND Flash类似的写控制字的方式。主控制器有16字节寄存器组,可以从I/O总线上读取指令和地址。指令寄存器采用存储器映射(Memory Mapped Register)的编址方式,也就是说,寄存器的地址统一编入内存空间,从0xFF0到OxFFA。

3.2主控制器的实现

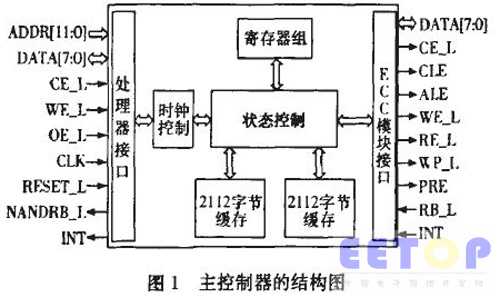

主控制器的结构框图见图1。下面分别讨论时钟控制模块和状态控制模块的设计实现。

(1)时钟控制模块。对于这种读写使能都是低电平有效的芯片,采用占空比为1:1的时钟进行读写操作对提高数据的存取速度并不划算。比如,进行读取操作时,RE_L至少要保证低电平35ns才能保证数据被正确读取,RE_L上升为高电平后只要保证数据再被保持10ns的时间就行,这样加上5ns的余量,时钟周期至少也要为80ns。为r保证数据能够被正确读取,并尽量提高读取速度,我们采用16.7MHz即周期为60ns,占空比为1:2的时钟。这种情况下,低电平持续时间为40ns,35ns数据确信被读取后,仍有5ns的余量,高电平有20ns时间,也很充裕,既保证了数据的正确读取。又充分发挥了器件的性能。

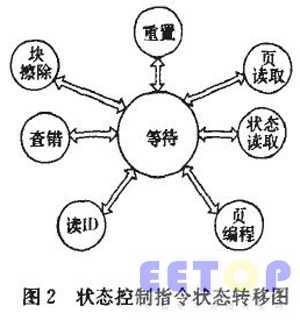

(2)状态控制模块。如图2所示,主控制器执行可控制

NAND Flash进行重置、块擦除、页读取、查错、读ID。页编程和状态读取指令的操作,不支持对NAND Flash的随机读写操作。当地址输入为0xFFA时,指令寄存器中的命令字就会被读取,确定下一步要执行的指令,然后转移到相应的状态。

4 ECC模块

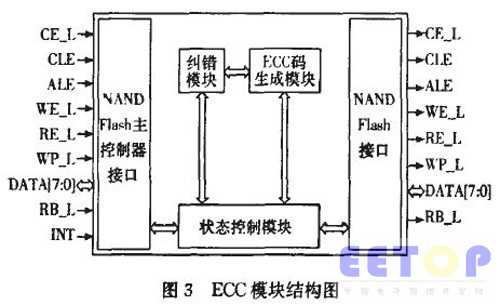

NAND Flash器件都受位交换现象的困扰,在某些情况下一个比特位会发生反转。本节论述了专用校验算法ECC(Error Correction Code,简称ECC的设计实现过程。ECC模块被置于NAND Flash器件和主控制器之间,ECC模块从主控制器接收各种信号,不需要工作时直接将收到的信号传给NAND Flash。需要工作时截取主控制器的控制信号,加七自己的操作后再传给NAND Flash。ECC模块结构见图3。

(1)校验码生成模块。ECC校验码生成模块有96比特(12字节)的运算寄存器供运算时暂存数据,分成四组每组三字节的寄存器,这些寄存器保存着奇偶校验值(也就是各位的异或值),每当数据送人时这些寄存器的值就更新一次。这些奇偶校验标志的计算基于每字节数据的顺序位置及数据本身。

(2)纠错模块。当NAND Flash进行读操作时,读出的数据将会被ECC码生成模块重新计算ECC码。当主控制器读完一页的所有2 010字节数据后,ECC模块开始读取事先写入的FffX2校验码,这些校验码按字节移人查错模块的移位寄存器中。当3字节校验码移入寄存器后,查错模块将其与新牛成的ECC码做异或运算并确定错误类型及位置,同时将错误信息存入一个14位的寄存器中。

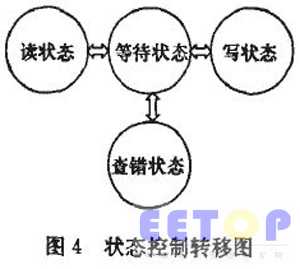

(3)状态控制模块。ECC模块的状态控制部分控制整个ECC模块的工作时序,见图4,同时根据当前的状态信息输出状态信号。对于读操作,计算一次ECC码需要512字节,因此每次至少要读出512字节的数据。为简单起见,我们只对N趟蛔Flash进行整页的读操作,总线上传输前2 048字节数据时,ECC模块计算ECC码,传后12字节数据时,ECC模块将其存下,待数据传输完毕后进行校验,将存下的E(℃码与计算出的ECC码进行按位异或,确定数据的正确性。对于写操作,与读操作类似,写操作也要以整页为单位进行。数据一边传入NAND Flash,ECC模块同时计算ECC码。当主控制模块传人第2 010字节数据后,ECC模块接管数据总线,将自己计算出的ECC码传人NAND Flash。对于查错操作,当主控制器下0x23指令时进入该状态。将每页2 048字节数据共产生的8字节错误信息,包括错误的位置及种类传送给主控制器,对于其它操作指令直接传给NAND Flash芯片。

5 控制接口电路的验证

对块擦除指令、页读取指令、页编程指令、重置指令进行功能仿真。地址0XFFA为指令寄存器,0x6代表块擦除,0x0代表页读取,0x8代表页编程,0xF代表重置。仿真结果如图5~图8所示。通过和NAND Flash器件要求的时序图对比可以看出,控制器输出的信号完全符合器件的要求。

6 结束语

本文在分析了NAND Flash产品特性的基础上,给出了NAND Flash控制接口电路的设计方案和验证结果。本文的创新点是采用同步设计和FSM设计方法,控制接口电路能够正确地将以SRAM时序输入的块擦除、页读取、页编程、ID读取、重置、状态读取操作指令转化为NANDFlash器件要求的操作时序,大大简化了NAND Flash的读写控制时序。另外,接口控制电路还能实现ECC功能,具有512个字节中发现2比特错误、纠正l比特错误的检错纠错能力。接口控制电路的各个指令操作功能在Xilinx的Spartarr3 Board上得到了验证,工作最高频率达到100MHz。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网