来源:现代电子技术 作者:王创伟 原 亮 丁国良 尹文龙 常小龙

引言

近年来,现场可编程门阵列(Field Programmable Gate Array,FPGA)由于其高性能、低价格、高开发速度、方便的编程方式等特点得到了广泛的应用。但对FPGA进行DPA(Differential Power Analysis,差分功耗分析)攻击已经成为FPGA应用中信息安全的主要威胁之一,受到了广泛的关注。

DPA是SCA(Side Channel Attacks,旁路攻击)技术的一种,其攻击思想为:以电路的功耗特性为基础,利用功耗与内部密钥的关系,将大量采样到的包含该内部密钥运算的功耗波形数据根据所猜测的密钥进行划分,使得所划分的两部分具有不同的功耗特性。最后,对两部分的功耗数据相减得到功耗差分曲线,如果猜测正确,差分曲线将出现明显的尖峰。

因此,进行DPA攻击的根本原因是电路逻辑表示的不对称性引起的。本文将应用FPGA的自身结构特点,结合目前常用的抗DPA攻击的电路级防护技术,深入研究与分析在FPGA平台上实现针对DPA攻击的电路级防护技术。

1 FPGA上的电路防护技术

1.1 FPGA的底层结构

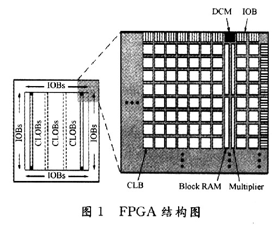

FPGA的简化结构如图1所示。FPGA内部最主要的、设计工程中最需关注的部件是CLB(Configurable Logic Block,可配置逻辑块),IOB(Input/Output Block,输入/输出块),Block RAM(块RAM)、DCM(Digital Clock Manager,数字时钟管理器)和Multiplier(乘法器)。其中CLB是FPGA具有可编程能力的主要承担者,Virtex-5的一个slice的主要组成单元包括4个6输入查找表、4个触发器和若干个选择器。

1.2 双轨电路技术的实现

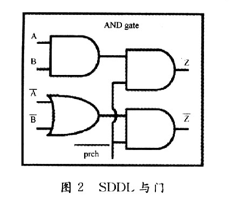

双轨电路技术是指无论是输入还是输出都是用两根线来表示的。由图2可见,在SDDL与门中,信号A就由A和 共同表示,而输出Z也由Z和

共同表示,而输出Z也由Z和 表示。在这种表示下,一个变量可以有4种不同的逻辑值(0,0),(0,1),(1,0)以及(1,1)。SDDL将(0,1)和(1,0)分别用来表示逻辑0和逻辑1。这样电路内部的逻辑0和逻辑1就变成了对称的,从而使得各自的功耗相同。另外,逻辑门还引入了一个prch预充电信号。在prch有效的情况下,输出是(O,0),这个值也就是变量为预充电时在电路中的表示方式。电路的工作分为两个状态:运算状态和预充电状态。这两个状态交替更换,也就是在prch上加载一个固定周期的脉冲。如此一来,电路中变量值的变化就是(0,O)到(O,1)或(1,O),或者是(0,1)或(1,0)到(O,0),每次翻转都是只有一根信号线进行翻转。逻辑O和逻辑1达到了完全的平衡。

表示。在这种表示下,一个变量可以有4种不同的逻辑值(0,0),(0,1),(1,0)以及(1,1)。SDDL将(0,1)和(1,0)分别用来表示逻辑0和逻辑1。这样电路内部的逻辑0和逻辑1就变成了对称的,从而使得各自的功耗相同。另外,逻辑门还引入了一个prch预充电信号。在prch有效的情况下,输出是(O,0),这个值也就是变量为预充电时在电路中的表示方式。电路的工作分为两个状态:运算状态和预充电状态。这两个状态交替更换,也就是在prch上加载一个固定周期的脉冲。如此一来,电路中变量值的变化就是(0,O)到(O,1)或(1,O),或者是(0,1)或(1,0)到(O,0),每次翻转都是只有一根信号线进行翻转。逻辑O和逻辑1达到了完全的平衡。

1.3 预充电技术的实现

普通逻辑门不能提供持续转换活动,逻辑门的输入不变将导致门的数据独立。解决这个问题要通过增加预充电电路来提供变换。当时钟为高时,连接预充电电路输入一个预充电相位,连接点变化到逻辑O;当时钟为低时,电路输入计算相位,实际计算完成。在FPGA上采用预充电逻辑的目的是要求在预充电相位期间slice的输出必须是逻辑O,有两种方式来完成。在一个Xilinx的slice中,每个LUT后跟着专门的多路选择器和内存单元,可配置为寄存器或锁存器。这里考虑使用多路复用器和内存单元来实现预充电,每种方法各有优点和缺点:

(1)使用时钟控制的多路复用器来实现预充电功能。将每个片子中单独的内存单元作为寄存器,但是除了寄存器的普通时钟还要分配一个反向时钟。这种方法的缺点是复制一个时钟信号并生成直接和互补信号将明显增加功耗和电路面积,布线也将复杂化。

(2)使用内存单元作为带有反向使能输入的异步清零锁存器来实现预充电功能。只需要一个单独信号给寄存器和预充电锁存器,预充电功能由连接反向使能输入和锁存器的清零输入实现,使用这种方法的缺点是专门设计的寄存器存储器需要一个单独的slice。

2 DES加密模块的实现

要在FPGA上实现安全防护结构来确保关键部件的功耗恒定。这里选择从双轨和预充电技术在FPGA上实现旁路安全防护逻辑。当前的技术水平需要在FPGA上进行精确控制布局和布线。下面从S盒硬件宏的实现和DES加密核的实现来介绍基于FPGA的DES加密模块实现。

2.1 S盒硬件宏的实现

S盒的设计是DES算法关键部分,S盒设计的优劣将影响整个算法性能。在采用FPGA实现时,应从资源和速度的角度出发,有效利用FPGA可配置属性,充分考虑器件内部结构,尽可能使两者都达到最优。在设计中,由于综合工具的介入,所输出的网表很难被设计者所理解,同时要找到一种更好的方法来控制组合电路,因此要建立硬件宏模块,简称硬宏。这与传统的设计流程不同之处是要充分利用:FPG Editor的功能,目的是从FPGA底层结构的配置上实现双轨和预充电技术。

通过Xilinx提供的FPGA Editor工具,首先读入布局布线后输出的NCD文件,并将其转化为新的NVD文件,再送往BitGen软件,进行布局布线的优化,最终在FPGA内部来建立目标电路,把它存为一个宏文件便于在上层进行调用。要注意两个问题:建立硬宏需要进入到slice内部,准确控制Slice内部的器件选择和器件之间的连线,防止设计出错;宏的功能验证要建立仿真模型,直接编写一个行为仿真模型后在上层设计中调用这个仿真模型,要确保仿真模型和宏之间的一致性。

2.2 DES加密核的实现

DES算法的基本流程如下:首先,输入明文通过初始置换,将其分成左、右各为32位的两个部分,然后进行16轮完全相同的运算。经过16轮运算后,左、右半部分合并在一起经过一个末置换(初始置换的逆置换),于是整个算法结束。在每一轮运算中,密钥位移位,然后再从密钥的56位中选取48位。通过一个扩展置换,将数据的右半部分扩展为48位,并通过一个异或操作与一个48位密钥结合,通过8个S盒将这48位替代成新的32位数据,再通过一级置换操作,这四步操作即为函数f。

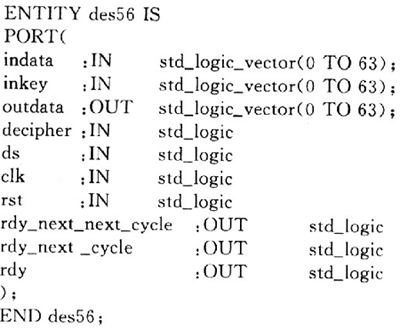

S盒是DES中的非线性模块,直接决定DES算法的安全性。在函数f的实现中,采用上面的思路,使用例化调用了S盒。DES加密核的VHDL设计思路如下:首先调用库函数构造ROM,然后使用VHDL语句进行行为描述。这种方法要结合器件的内部结构,对于小容量的ROM采用数组描述,大容量的ROM应采用元件的方式来实现。在VHDL设计中,库函数、子程序的调用以及元件的调用和使用间接变量,都是影响速度的主要因素。由此得到DES Core的接口定义如下:

3 攻击实验的对比与分析

3.1 FPGA加密芯片攻击试验平台建立

目前FPGA的种类很多,但其中有大于50%的份额被Xilinx公司抢占,在此选用xilinx公司的Virtex-5(ML501),对其他种类的FPGA的攻击和此类似。

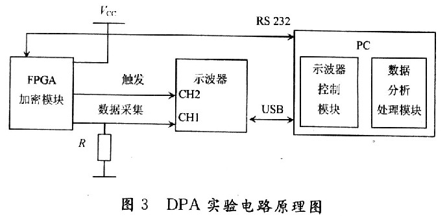

ML50l在工作时需要3个工作电压:内核电压(1.2 V)、辅助电压(2.5 V)、I/O电压(3.3 V),而ML501芯片的所有地线是并结在一起的。对FPGA攻击的实验的原理图如图3所示,示波器(Tektronix DP04104,1 GHz BW,5 Gsample/s)的2通道接收Virtex-5(ML501)加密模块的触发信号,在内核电压和芯片之间置一个电流探针(Tektronix CT-2,1.2 kHz~200 MHz),1通道用电流探针测试内核的功耗变化。攻击过程如下:在PC机上生成64位随机明文,通过串口发送至FPGA。FPGA收到明文后利用存储在其中的密钥对明文进行DES加密,并在第16轮加密操作时对示波器产生数据采集的触发信号。在进行数据采集时其实质是要采集内核电流所引起的功耗变化,并将数据通过USB总线送至PC机,最后在PC机上运行分析程序攻击出64位的密钥。

3.2 对FPGA加密芯片的攻击

设定明文输入和电流数据采样为500组,采样深度100 000点,采样频率为500 MSPS,在相同的试验环境下,对带有防护结构和不带防护结构的两种DES的加密结构进行功耗测量,同时根据密钥的推测将明文分类,计算各类的平均功耗,然后相减,可以得到差分功耗分析曲线。试验后发现对不带防护结构的ML50l FPGA芯片进行攻击时,当子密钥块猜测正确时,功率差分曲线出现明显的尖峰,采用相同的方法可以攻击出其他子密钥块,由此可以获取第16轮的子密钥K16(48位),攻击成功。对带防护结构的芯片攻击时,功率差分曲线基本是平缓的,波动非常小,也没有明显的尖峰存在,可见DPA攻击对带有防护结构的FPGA无效。

4 结语

由以上DPA攻击试验表明了FPGA实现DES加密算法对DPA的脆弱性,而采用双轨和预充电防护技术的FPGA加密芯片具有较好的抗DPA攻击能力。这也说明利用FPGA底层开发工具通过硬件宏方法能在FPGA硬件上实现安全防护技术的拓展,对开展芯片的安全防护工作的研究具有重要意义。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网