作者:David J. Easton

DesignVerify 公司创始人

david.easton@designandverify.com

许多FPGA设计都采用高速存储器接口,可能调试比较困难,不过只要采用正确的方法就能成功进行调试。

现代FPGA通常连接高速SRAM和SDRAM存储器。要确保这种器件无差错运行,调试起来可能比较困难。我们必须确保包括电路板布局、电源和FPGA中存储器接口电路等诸多因素准确无误,才能实现一款切实可行的存储器设计。

您在调试SRAM和SDRAM存储器时可能会遇到一些问题,而这些问题有可能会让您头疼好几天。设计和调试高速存储器接口时必须确保采用适当的调试方法。下面我将介绍的高效设计流程模型采用的是赛灵思Virtex®-4和Virtex-5 FPGA,然而Virtex-6和7系列器件也同样存在问题和相应的解决方案。我和同事采用赛灵思存储器接口生成器(MIG)工具来生成所有的存储器IP核,并通过赛灵思ISE®工具来进行设计的综合和布局布线。在详细分析特定设计的特性之前,我们不妨先来看看赛灵思MIG工具、针对赛灵思FPGA的存储器校准过程以及我们用来验证存储器接口设计的内建自测试(BIST)电路。

赛灵思存储器接口生成器

赛灵思提供存储器接口生成器工具为其FPGA器件生成存储器接口内核。

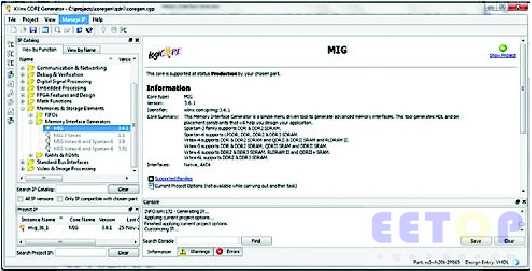

从赛灵思CORE Generator™调用的MIG工具可为DDR-II SRAM、DDR2 SDRAM和QDR-II SRAM等各种类型存储器生成接口。图1显示了赛灵思CORE Generator屏幕截图,详细介绍了MIG3.6.1中支持的赛灵思器件系列和存储器。此外,还有一款7系列MIG工具可支持赛灵思最新器件。

MIG通过图形用户界面(GUI)输入存储器和FPGA类型的详细信息,最后生成VHDL语言或Verilog语言的寄存器传输级(RTL)文件,以及有关存储器接口的用户约束文件(UCF)。您可将这两类文件与设计方案的其它部分进行综合。此外,MIG还可生成基础架构模块,为存储器接口提供所需的时钟和复位。此外,该工具还提供测试平台电路,可用来生成存储器器件的读写操作,以验证正常运行。您可从赛灵思网站下载MIG工具及其支持的FPGA和存储器的完整介绍。

校准注意事项

为了确保从存储器准确捕获数据到FPGA中,存储器接口内核应在使用读取数据路径前对其进行校准。校准过程在加电时自动进行。基本而言,数据训练模式被写入到存储器中,随后不断读回。这是过程分三个阶段:第一阶段要让读取数据窗口相对于数据选通信号居中,对进入FPGA的数据进行计时;第二阶段要确保居中的数据和时钟同步于FPGA时钟域,从而使数据能在输入触发器和FPGA架构中的触发器之间传输;第三阶段则提供读取验证信号。赛灵思MIG文档全面介绍了各种不同类型的存储器校准过程。

图1- CORE Generator MIG工具支持多代赛灵思FPGA。

时钟生成器和内建自测试电路(BIST)

我们采用赛灵思MIG工具生成所有存储器接口设计。不过在一些设计实例中我们则不用MIG工作流程。我们使用的FPGA所在的电路板是针对各种用户和应用设计的。因此我们要设计一个定制时钟生成器与复位模块,提供用户应用所需的所有时钟和复位。这意味着应移除MIG生成的基础架构模块并从我们的定制模块为存储器接口提供时钟和复位。

此外,我们还设计自己的定制BIST模块,用来对存储器进行全面的测试,这就要通过使用各种数据模式读/写每个存储器的位置,包括0、F、A、5、walking 0、walking 1、顺序数据和伪随机二进制序列(PRBS)数据等。BIST电路在主机接口控制下运行并报告所发现的任何错误。BIST电路可存储所发现的任何数据错误的地址,并发出哪个或哪些数据位是错误的信号。图2显示了通用设计的方框图,MIG内核对应于电路板上特定的DDR-II SRAM、DDR2 SDRAM或QDR-II SRAM存储器。

需要反复强调的是,任何FPGA存储器接口要正常运行,就必须遵循FPGA和存储器的PCB布局建议。必须让器件之间的轨道长度相匹配,尽可能地减少偏移,同时也有必要尽可能地减少信号之间的串扰,为所有器件提供适当的去耦。FPGA和存储器有许多电源,通常采用开关稳压器和线性稳压器的组合方式进行供电,应根据制造商的产品使用指南确保所有这些器件正常运行。您虽然需要花时间研究FPGA和存储器的电源的原理图及布局方面的详细信息,但会显著缩短调试时间,可谓磨刀不误砍柴工。

下面,我们来进一步分析使用前述BIST电路测试中出现误码的三个存储器实例。全部实例均出现类似的症状,也就是在存储器成功校准后出现误码。然而每个实例中的出错的原因各异。我们通过反复运行BIST测试器发现了这些误码。还有一点需要指出的是,所有电路板都成功通过了JTAG测试。

实例1:连接DDR-II SRAM的VIRTEX-4电路板

该电路板采用的Virtex-4 FPGA连接了一个运行频率为200 MHz的 DDR-II SRAM存储器。在存储器接口成功校准后,并开始进行BIST测试时,出现了单误码。这种错误出现在不同的存储器位置和数据字中的不同比特位置。

我们所做的第一件事就是测量所有FPGA和存储器的电源,发现其都在正确的电压规范内运行。我们再检查电路板上的振荡器,其频率也正确,信号也没有过多的抖动。接下来我们决定在进行BIST测试时使用示波器再次检查电压。

存储器电源电压VDD采用1.8V稳压器供电,我们发现稳压器的输出电压出现过多的纹波,超出了存储器的电压规范要求。我们检查稳压器电路,发现其输出平滑电容的值不准确,仅为要求的10%。我们用准确的值加以替代,纹波下降至可接受的水平,这样输出电压就在规范要求以内,误码也消失了。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网