Xilinx日前宣布在20nm工艺节点再次推出两大行业第一:投片半导体行业,也是可编程逻辑器件(PLD)行业首款20nm All Programmable器件;发布第一个ASIC级可编程架构UltraScale。“我们制定了业界最激进的20nm投产计划。”赛灵思公司(Xilinx)全球高级副总裁汤立人(Vincent Tong)说,“我相信,当客户结合采用台积电技术和UltraScale架构,并通过Vivado设计套件进行协同优化后,其产品将比竞争对手提前一年实现1.5至2倍的系统级性能和可编程集成。”

此次推出ASIC级可编程架构的大背景在于,随着需要极高数据速率的400G OTN、LTE/LTE-A、4K2K和8K视频处理、以及数字阵列雷达等新生代系统的不断涌现,时钟歪斜、大量总线布置以及系统功耗管理方面的挑战将会达到令人生畏的程度。“一旦以数Gbps速度传输的串行数据流进入芯片,就必须扇出(Fan Out),以便与片上资源的数据流、路由和处理能力相匹配。”汤立人说。因此,实现上述要求的必要条件并非仅是改善单个器件性能,或增加模块数量这么简单,而是要从根本上提高通信、时钟、关键路径以及互联性能,以满足这些高性能应用对海量数据流和智能数据包、DSP或图像处理等的要求。

Virtex UltraScale 4x100G MuxSAR OTN交换

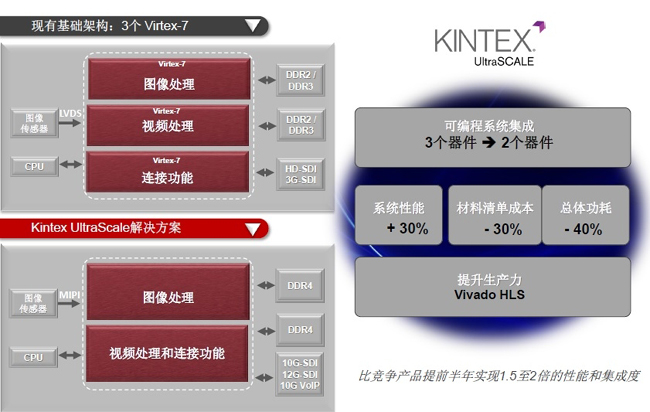

Kintex UltraScale用于超高视频处理

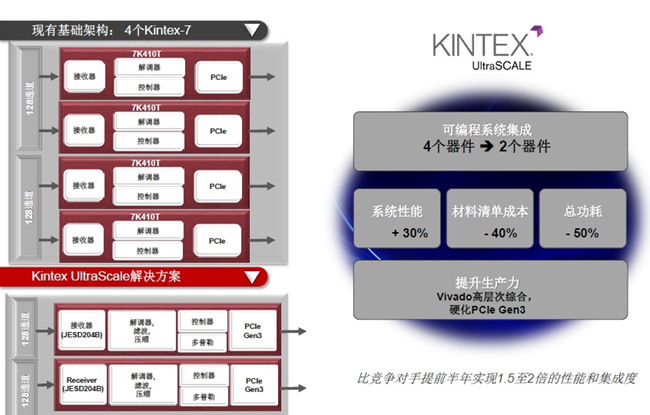

Kintex UltraScale用于256通道超声图像处理

此次赛灵思将精力重点放在了解和满足新一代应用对于海量数据流、多Gb智能包处理、多Tb吞吐量以及低时延方面的要求。最新开发的UltraScale架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。据称,它不仅能解决系统总吞吐量扩展和时延方面的局限性,还能直接应对先进工艺节点上的头号系统性能瓶颈—互联问题。

源于其中包含众多ASIC要素,赛灵思将UltraScale称为ASIC级可编程架构。例如,针对海量数据流而优化的宽总线支持多兆位(multi-terabit)吞吐量;多区域类似ASIC的时钟、电源管理和下一代安全性;高度优化的关键路径和内置的高速存储器串联,消除DSP和包处理的瓶颈;二代3D IC系统集成芯片间带宽的步进功能;高I/O和存储器带宽,提供动态时延缩短和3D IC宽存储器优化接口;Vivado工具消除布线拥堵和协同优化,器件利用率超过90%等。

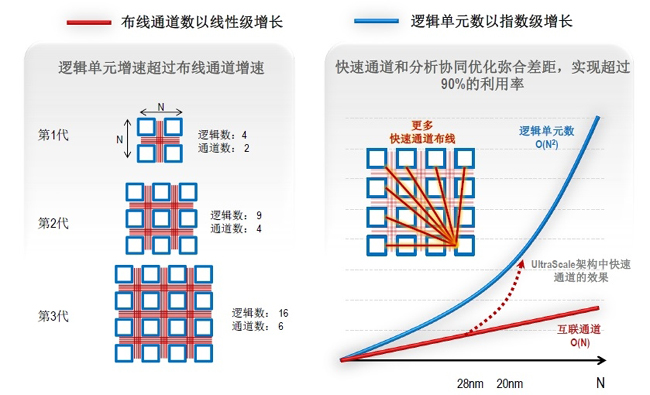

增加真实有效的布线通道有助于应对不断增加的复杂性

与前几代可编程逻辑器件所采用的时钟方案完全不同,Xilinx在UltraScale架构中加入了类似ASIC时钟功能,不但消除了放置方面的众多限制,还能够在系统设计中实现大量独立的高性能低歪斜时钟资源,而这正是新一代应用的关键要求之一。

提高布线率,为UltraScale架构引入类似高速公路设计中的快速通道理念,以缓解数据拥塞问题,则是本次发布的另一大亮点。这些新增的快速通道可供附近的逻辑单元之间传输数据,尽管这些单元并不一定相邻,但它们仍通过特定的设计实现了逻辑上连接。这样,通过UltraScale架构提供的高布线效率,就能够使可管理的数据量呈指数级上升。这意味着,只要设计合适,布局布线就没有问题。器件利用率将有望达到90%以上,且不降低性能或增加系统时延。

UltraScale架构引入类似高速公路设计中的快速通道理念

赛灵思设计UltraScale架构还有另一个目的,就是充分利用继20SoC之后的工艺节点16nm FinFET所提供的更高性能、容量和节电性能。另外,在赛灵思“FinFast”开发计划的支持下,赛灵思UltraScale架构和Vivado设计套件针对台积电16nm FinFET工艺技术进行了协同优化。这样,赛灵思与台积电将于2014年推出第二代UltraScale All Programmable器件芯片。

支持UltraScale架构FPGA的Vivado设计套件早期试用版现已开始供货,首批UltraScale器件将于2013年第四季度开始发货。今后,对于20nm和16nm工艺,相应的器件命名方式将更改为Kintex UltraScale、Virtex UltraScale和Zynq UltraScale SoC,应用目标锁定256通道超声、超高清视频处理、400G OTN交换、4X4混合模式无线电、ASIC原型设计等新兴领域。

作者:邵乐峰 来源:国际电子商情

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网