波波束形成是一种利用一系列传感器实现方向性、提高发送信号强度以及提升接收信号质量的信号处理技术。通信、雷达、对抗措施、武器系统、石油与矿产勘探、医疗成像及测向等领域均广泛使用了波束形成技术。

在测向应用中,我们通过控制波束形成天线来定位信号源的到达角。我们可以使用两组或两组以上的天线阵列来三角定位信号源的确切位置,这对于大量信号情报及反恐怖行动而言是必不可少的。这项技术的准确度取决于各波束形成通道之间增益和相位的精确设置。我们通过采用带有本地定制IP 的赛灵思Virtex-6 FPGA 构建的Pentek 产品来实现精细调节,从而达到提升系统性能和准确度的目的。

波束形成原理

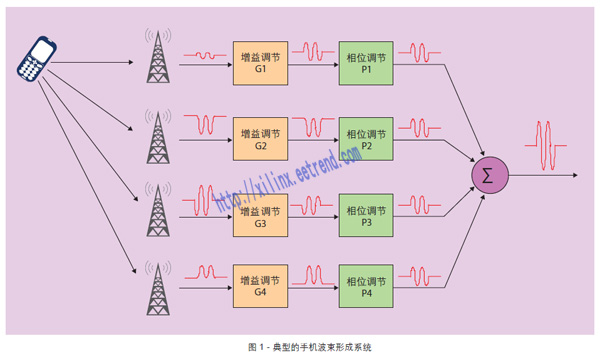

我们通常使用一系列传感器或天线实现的波束形成技术来提升特定方向上的接收性能(如图1 所示的手机某方向的接收性能)。来自信号源的信号根据信号源与天线之间的距离依次到达每根天线,这样天线信号之间就会有相对的相位及振幅偏移。

在波束形成过程中调节每个天线信号的增益和相位,可补偿信号路径上的不同延迟。调节方式就是将来自每根天线的信号与来自某个特定方向的信号同步。当信号相加时,来自其它方向的非定向信号就会相互抵消,而来自波束形成方向的信号则会进行有益的累加,从而显著提升信噪比。在这种调节方法中,通过采用电子方式调节每条路径上的增益和相位,我们有效地将天线转向信号源的方向。

八通道系统

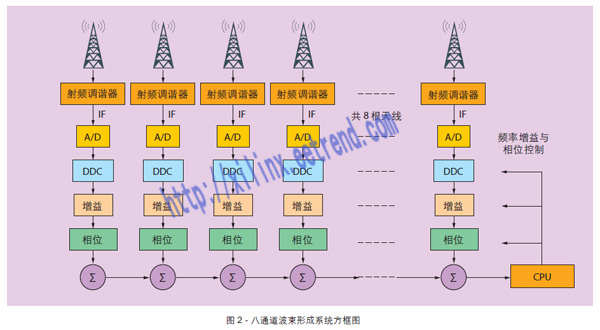

在这个系统中,我们按线性阵列布置了8 根天线,如图2 中的整体方框图所示。这里的天线频率为2.5GHz,所以每个天线信号都需要先进行放大、滤波,然后通过降频转换为中频(IF),这样模数转换器才能以合适的采样频率完成信号的数字化。为保持波束形成的固定相位关系,所有8 个通道均必须采用同步采样。

随后我们在数字下变频器(DDC)中将从每个模数转换器的信号采样降频转换为基带的复杂I+Q 信号,其中也涉及了针对波束形成“权重”的特定通道相位及增益调节。最后我们在总和模块中将所有八个基带信号相加,可生成波束形成总和信号。CPU 分析该总和信号,并对相位及增益系数进行调节,从而跟踪或适应新的目标。

FPGA 能够访问开发板上所有数据及控制路径,支持诸如数据多路复用、通道选择、数据打包、门控、触发及存储器控制等工厂预装功能。其中的每种功能均以IP 模块形式存在。

PENTEK 模型53661 波束形成板

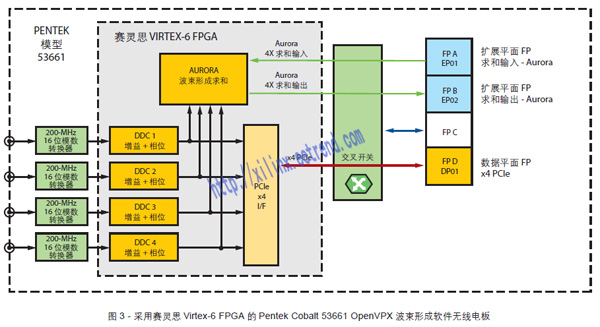

Pentek 模型53661 软件无线电板是一种3U OpenVPX Cobalt 开发板,如图3 的简化方框图所示。它采用了4 个200MHz 的16 位模数转换器,一个时序、时钟同步单元以及赛灵思Virtex-6FPGA。

FPGA 能够访问开发板上所有数及控制路径,支持诸如数据多路复用、通道选择、数据打包、门控、触发及存储器控制等工厂预装功能。Cobalt 架构将FPGA 构建成某种适用于数据处理应用的容器,其中的每种功能均以IP 模块形式存在。

我们可以使用LX240T、LX365T、SX315T 及SX475T 等各种不同的FPGA 来实现处理任务的特定要求。SXT 器件拥有多达2,016 个DSP48Eslice,理想适用于发送与接收之间信号的调制/ 解调制、编码/ 解码、加密/ 解密及通道化。

FPGA 在工厂预装有4 个DDC IP核,每个核均能够从4 个模数转换器的任何一个中接收模数转换采样。每个DDC 的抽取范围是2K-64K,能够提供2.5KHz-80MHz 的下变频基带带宽。每个DDC 均具有可编程增益和相移控制功能,能够跨整个VPX 背板访问处理器。在本系统中我们将为每个DDC 分配一个模数转换器。

每个DDC 输出处均有一个用于计算下变频信号功率的功率计。每款功率计都配备一个阈值检测器,以便在输出功率超过上限阈值或低于下限阈值的时候生成系统中断。这些功能可显著简化增益校准及信号监测工作,从而解决了系统处理器只能在软件中才能完成的难题。

此外,53661 FPGA 还包含一个本地Aurora 总和模块,可将四个DDC 输出加在一起,实现波束形成所需的通道组合。Aurora 是一种面向赛灵思FPGA 的轻量级链路层的千兆位串行协议。在这个开发板上,Aurora 接口通过4 个串行链路(4X)在一个输入端口上接收传输来的总和,并在4X 输出端口上交付包含4 个板载通道内容的新的传输总和。每个4X 链路运行在3.125Gbps 的时钟比特率上,数据传输率可达1.25GBps。

一个串行时钟速率为2.5Gbps 运行的本地PCIe x4 接口IP 为面向DDC 及波束形成参数编程的控制处理器提供了一个1GBps 速率的链路。此外, 该PCIe 链路还为交付4 个DDC 输出和波束形成总和输出提供支持。

可编程千兆位串行交叉开关将两个4X Aurora 总和链路与x4 PCIe 链路连接到VPX P1 背板连接器上。这种交叉开关具有高度的灵活性,能够让53661运行在各种OpenVPX 背板拓扑结构及插槽配置下。在本系统中, 我们将Aurora 链路映射到OpenVPX 扩展平面上。同样我们还可将PCIe 接口映射到发挥控制平面作用的OpenVPX 数据平面上。

八通道 3U OPENVPX 波束形成系统

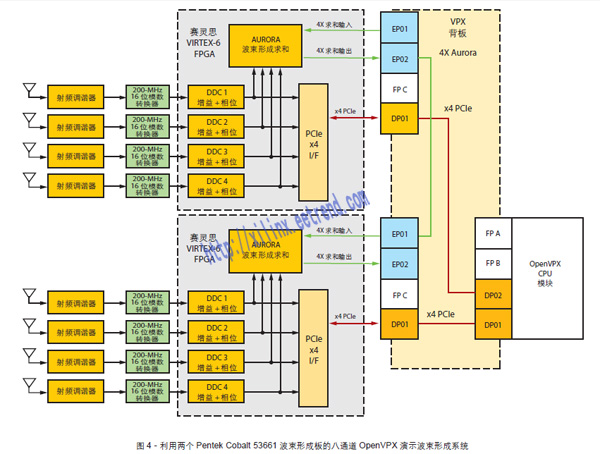

如图4 所示为完整的八通道OpenVPX波束形成系统。两块模型53661 开发板安装在OpenVPX 背板的插槽1 和插槽2,CPU 开发板则安装在插槽3。8 个适用于接收2.5GHz 信号的偶极天线为包含低噪声放大器、本地振荡器和混频器等在内的射频调谐器反馈信号。射频调谐器将2.5GHz 天线频率信号转变降为50MHz 的IF。

200MHz 16 位模数转换器负责数字化IF 信号,执行进一步降频转换为基带的工作,使用的DDCS 抽取为128。这样可提供I+Q 复杂输出样片,带宽大约是1.25MHz。每个通道的相位和增益系数用于控制阵列的方向性。

VPX 插槽3 中的CPU 开发板通过两个x4 PCIe 链路,又称OpenVPX“粗管”跨越背板发送命令和系数。

我们在VPX 插槽1 中的53661 开发板的左上部分处理前4 个信号通道,然后这4 个通道的波束形成求和值通过4X Aurora 求和输出链路跨越背板传输到插槽2 中的第二个53661 开发板的4X Aurora 求和输入端口。然后将第二个53661 开发板的四通道本地总和与第一块开发板传输来的总和再相加,就可得到完整的八通道总和。这个总和经由x4 PCIe 链路发送到插槽3 的CPU 卡。

模型53661 开发板上的3 个OpenVPX 4x 链路(OpenVPX 粗管)的分配通过使用前一方框图中的交叉开关进行简化。这样53661 就可以搭配各种不同的背板运行。由于OpenVPX 不约束跨背板链路的串行协议的使用,系统支持的混合协议架构如图所示。

波束形成演示系统

Pentek 的工程师已经建立起一个八通道波束形成演示系统, 配备了一款在Windows 下CPU 开发板上运行的控制面板。自动信号扫描仪可检测来自测试发射器的最强信号频率。该频率的中心是射频下变频器的50MHz IF 频率。一旦发现该频率,8 个DDC 就会进行相应的设置,将该信号降为0Hz,以便于求和。此外,控制面板软件还可实现8 个通道所有参数的特定硬件设置,包括增益、相位和同步延迟等。

另外一部显示器显示阵列的波束形成模式。通过调整8 个通道的相移,最大限度地提高与阵列平面垂直的-90°~ +90°整个到达角范围内的灵敏度,从而形成显示内容。

将理想八元件阵列在信号到达角为0°(直接来自阵列正前方)时的理论七波瓣图与实际坐标图进行比较。波瓣图下方是极坐标图,显示的是指向计算到达角的单个矢量。这个矢量是通过确定具有最大响应的波瓣而得到的。

此外还显示了布置在显示器正前方,作为信号源的现实发送器的实际坐标图。在这种情况下,理想的波瓣图受到物理对象、反射、线缆长度变化和天线细微差别的影响。不管怎样,定向信息的计算比较理想。随着信号源在阵列前的左右移动,峰值波瓣也随之移动,从而改变计算出的到达角。

该演示系统现已通过Pentek 在线提供。如果读者希望观看现场演示,敬请访问 http://pentek.com/go/xcellbf 。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网