当今复杂的 FPGA 含有众多用于实现各种电路与系统的功能块,诸如逻辑阵列、存储器、DSP 模块、处理器、用于时序生成的锁相环 (PLL) 和延迟锁定环 (DLL)、标准 I/O、高速数字收发器以及并行接口(PCI、DDR 等)。这些不同的功能块通常由多个时钟驱动,FPGA 一般会综合采用外部振荡器以及内部 PLL 与 DLL来生成时钟。系统设计人员必须决定如何综合使用外部与内部资源来实现最佳的时钟树设计。而可编程时钟振荡器用作 FPGA 系统的时序参考,可提供一系列优势。其中首要优势是为了实现时钟树优化而进行高分辨率频率选择时所带来的设计灵活性。另一个巨大优势是具有可以减少电磁干扰 (EMI) 的扩频调制功能。

内在可编程的硅 MEMS 时钟振荡器架构能够帮助采用 FPGA 的系统设计人员解决许多难题。这种微型机电系统架构能够轻松整合一些其它功能,如:用于消减 EMI 的扩频时钟、用于消除抖动的数控振荡器以及高速应用中的失效保护功能。

频率选择

一般系统需要一系列时钟频率。其中一些是标准频率,这种标准化可能是出于对行业规范强制要求的考虑(如:PCI Express要求的 100MHz 频率),也可能是由于得到了广泛的应用(如:用于 SATA 的 75 MHz 或用于 PCITM 的 33.333 MHz)。上述频率与 I/O 接口关联在一起,以确保实现互操作性,因为接口两侧可能不属于同一系统。与此相对,用户可选择用于驱动处理器、DSP和状态机引擎的时钟频率,以优化速度、功率或资源占用。

在进行速度优化时, 应以最高时钟频率来驱动处理引擎,以使每秒运算次数达到最高。但是,时钟周期抖动必须足够低,以确保最小时钟周期大于设计的临界时序路径,否则有可能出现逻辑错误。频率选择的常用方法是采用内部 FPGA PLL 对来自标准外部参考振荡器的高频时钟进行综合。此方法只有在内部 PLL 具有高频分辨率和低抖动时才有效。

某些 FPGA 集成了内部低噪声分数PLL,可满足所有这些要求。在这种情况下,可以采用简单的外部振荡器参考。不过,许多情况下 FPGA 会采用带有环形 VCO 和整数反馈分频器的 PLL 来综合不同频率。这种 PLL 小巧灵活,比较容易设计和控制,而且功耗极低。不过,使用此类内部 PLL 时很难同时实现高分辨率与低抖动。

图 1 为整数 PLL 的一般架构。对PLL 输出频率的编程需综合采用预分频器 (P)、反馈分频器 (M) 和后分频器 (N)来完成,如下式所示:

PLL 反馈环路形成一个限带控制系统。输出周期抖动主要取决于参考时钟相位噪声 (PNin ) 和内部 VCO 相位噪声(PNVCO),如下式所示:

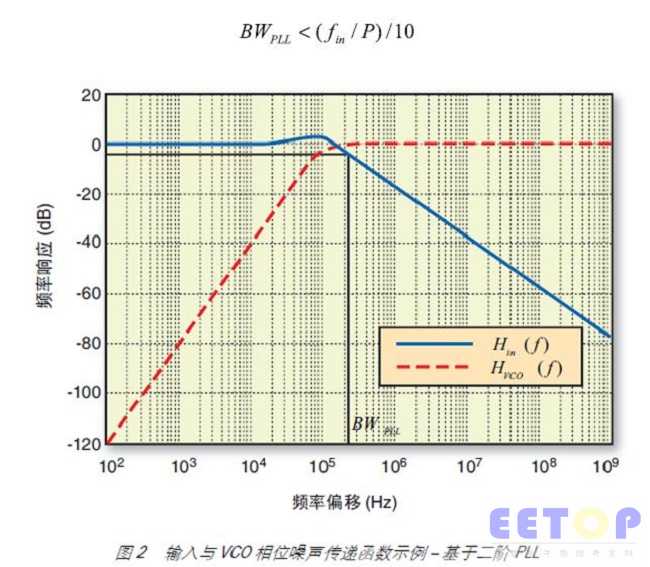

输入参考时钟相位噪声和 VCO 相位噪声与输出相位噪声息息相关,分别通过低通滤波器和高通滤波器响应来体现,如表达式中的 Hin 和 HVCO。HVCO 与 Hin 的截止频率直接相关。图 2 说明了典型二阶 PLL 中 Hin 与 HVCO 的相互关系。最高 PLL 带宽取决于相位检测器的更新速率。大部分实际 PLL 的最高实际带宽极限如下式所示:

例如,如果 PLL 输入频率是 40MHz并且 P=40,则最高实际 PLL 带宽是100kHz。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网