l 引言

频率合成技术的应用,对通信、数字电视、卫星定位、航空航天、雷达、电子对抗技术的发展起到了至关重要的作用。而作为波形发生器的核心的频率合成技术,其原理是把一个或多个高精度、高稳定性的参考频率,经过各种信号处理技术,生成同样精度和稳定性的各种离散频率。虽然各个芯片厂推出了先进的高性能、多功能DDS集成芯片,但在某些情况下,这些DDS集成芯片的控制方式、频率和转化率不符合系统要求。如果使用高性能的FPGA器件来代替DDS集成电路,便可以满足设计要求。

本文设计了一种低频信号发生及分析系统。本系统以高速可编程逻辑门阵列FPGA为核心技术,由FPGA通过p核产生双路低频信号,参数由按键输入。产生的双路信号经过加法电路的叠加,由FPGA对信号进行快速傅里叶变换得到频域信号,最后通过示波器观察频域信号,通过门限法得到该信号的频率和幅度等参数并在LCD上显示。该系统具有体积小、携带方便、操作简便、易于连接,采样率、数据传输速率高,动态范围大(12位A/D采样率)等特点,使用自制的线性电源,非常方便低频信号生成和分析。

2 系统组成与工作原理

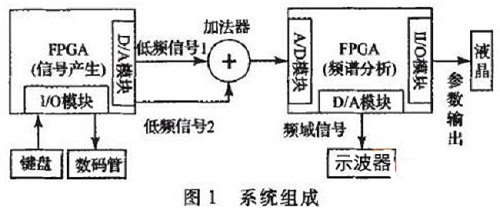

系统由FPGA核心板、D/A转换电路、加法器电路、A/D转换电路、直流稳压电源、键盘和显示等部分组成。

系统总体框图如图1所示。

双路低频信号由一块FPGA产生,通过按键控制频率、幅度等参数,参数实时显示在数码管上,2路信号送入加法器进行求和,然后经过A/D采样给另一块FPGA,并对信号进行快速傅里叶变换处理后提取出频域信号,频谱图可以通过示波器观察,最后分别显示叠加前两路正弦信号的频率和幅度。

3 硬件电路板设计

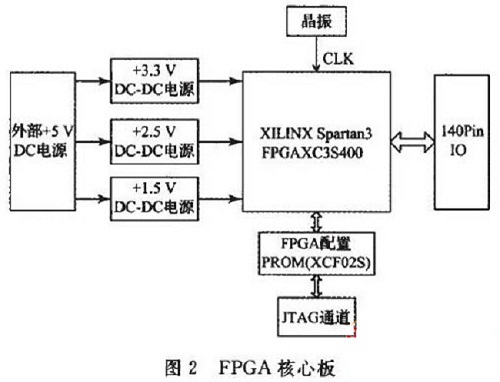

3.1 FPGA核心板设计

FPGA核心板担负着数据发送和分析的任务,是本系统最为关键的部分。FPGA核心板采用的是Xilinx公司Spartan3系列的XC3S400一PQ208型40万门芯片,其配置芯片为Xilinx公司的专用配置PROM芯片XCF02S,以实现加电自动配置。核心板采用5 V输入,板上有两块LM317电源芯片分别输出3.3V和2.5V电压。板上采用40MHz有源晶振,能够满足高速设计要求。核心板140支I/0口全部引出,非常便于与外围器件的连接及系统的扩展。最小系统框图如图2所示。

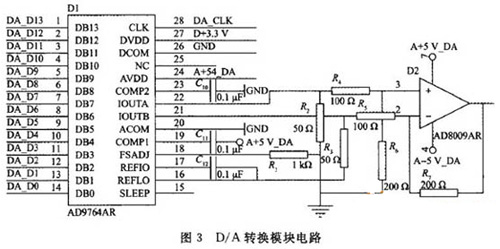

3.2 D/A转换电路设计

D/A部分采用14位模数转换芯片AD9764AR,双差分电流输出,差分操作不仅有助于消除与IOUTA和IOUTB相关的共模误差源,比如噪声、失真和直流偏置,而且为负载提供了两倍信号功率。电路如图3所示。

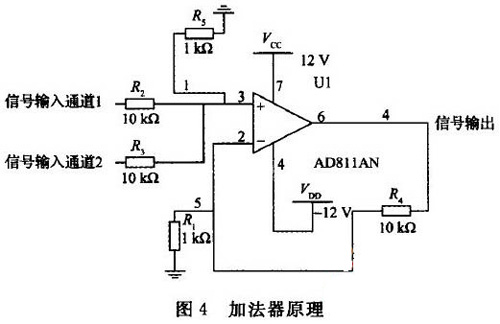

3.3 加法器电路设计

采用AD81IAN芯片求和电路如图4所示。

放大器的典型运算电路,两路信号求和输出。

根据计算公式:

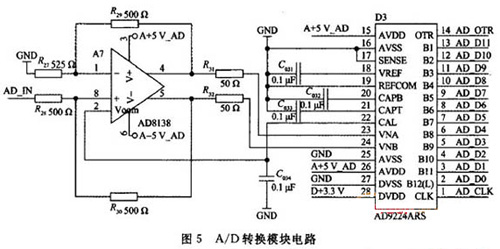

3.4 A/D转换电路设计

设计中采用ADI公司生产的快速A/D转换芯片AD9224.AD9224为28脚SOIC和SSOP封装的模/数转换器;内部采用闪烁式A/D及多级流水线式结构,因而不失码,使用方便、准确度高;在单一+5V电源下,它的功耗,仅有376 mw,信噪比与失真度为士0.7 dB,完全满足设计要求。AD9224应用电路如图5所示。

4 软件设计

4.1 软件总体设计

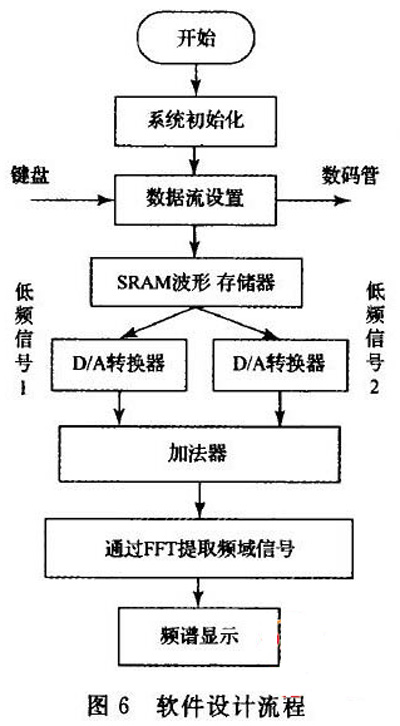

软件部分主要包括信号产生模块、人机交互模块、频谱分析模块。整个系统的详细设计流程如图6所示。负责产生信号的FPGA通过扫描按键得到参数,送给数码管显示,并调用IP核产生各种波形。输出信号的形状通过拨码开关控制负责信号分析的FPGA调用FFT核将频谱信号输出,并从频谱信号中将信号的频率和幅度参数显示出来。

4.2 信号产生模块设计

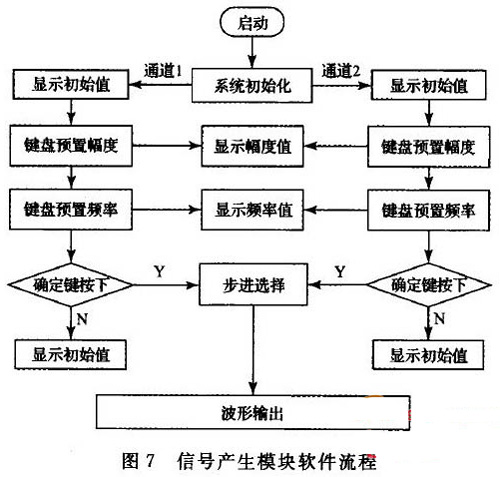

先通过DDS技术建立正弦波、三角波、锯齿波的IP核和包含占空比控制字的方波IP核。系统启动后,由通道扫描按键输出数值并送给数码管显示,按下确定键后赋给频率、幅度、占空比或相位差等参数控制字,并调用IP核产生各种波形,再通过拨码开关选择输出的波形。参数的步进由按键控制。该模块的详细软件设计流程,如图7所示。

4.3 频谱分析模块设计

4.3.1 FFT模块设计

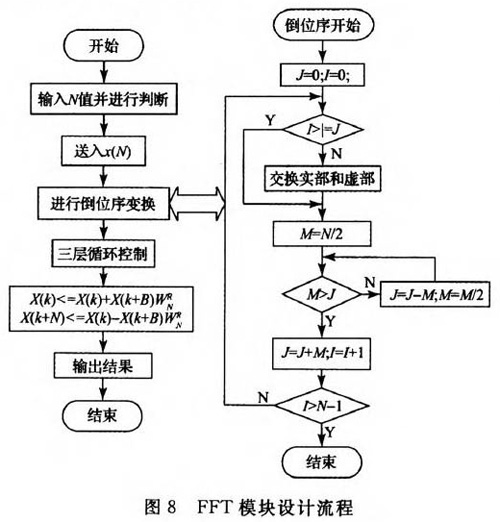

FFT算法的主要核心思想就是将N点的序列分解为(N一1)/2,直到2点的DFT.目前的算法可以从时域和频域分别将分解成不同的子序列,前者称为时间抽选法,后者称为频率抽选法∞3。所谓时间抽选法,就是直接将z(挖)逐次分解成奇数子序列和偶数子序列,通过球子序列的DFT而实现整个序列的DFT.频率抽选法是在频域内将x(愚)逐次分解为偶数点子序列和奇数点子序列。然后对分得越来越短的子序列进行DFT运算,就可以得到整个频域内序列的FFT流图。FFT模块软件流程图如图8所示。

4.3.2频率幅度提取模块设计

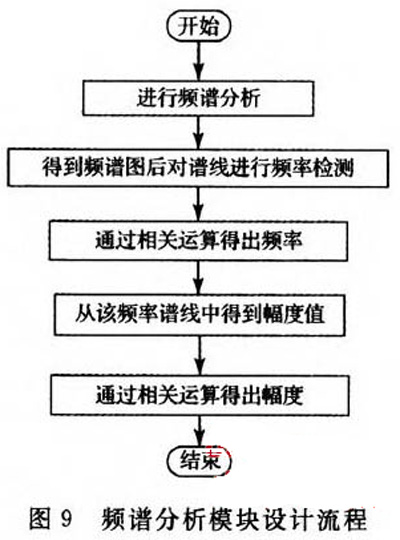

频谱分析时将参数提取过程分成频率提取和幅度提取2个阶段。原信号经过A/D采样后进入频谱分析系统,输出频域信号。其中频率提取采用过门限法,首先设定频率提取的门限值,当频点的幅值超过设定门限时,频率即被系统提取出来,同时进入幅度提取过程。在幅度提取阶段,通过算法找出幅值大小,该值即为原信号的幅度。具体实现流程如图9所示。

5 系统调试和测试

在系统硬件焊接完成及软件功能仿真、下载成功之后。接下来对整个系统进行调试,其过程如下:将信号产生部分的2个输出信号接入求和电路的输入端,再将求和后的信号输入频谱分析仪,最后将频谱信号送入示波器显示。观察示波器显示谱线与设置是否相符,并不断修正元器件参数和软件的的算法,以提高该系统的精度,避免理论与实际产生的偏差。

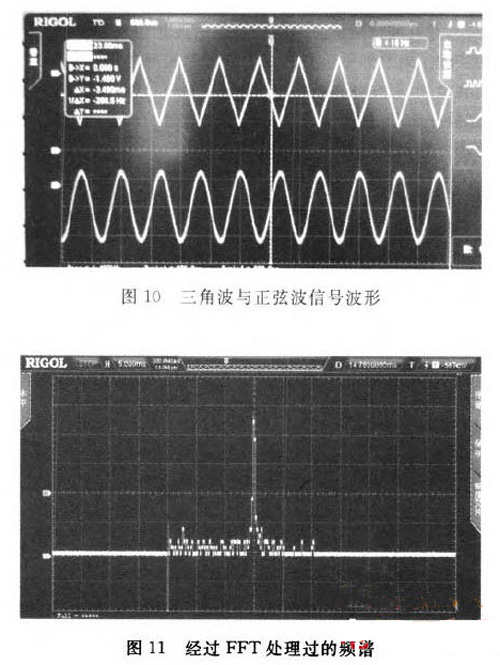

目前,本系统信号产生部分可以实现双路信号均可在正弦波、三角波、锯齿波、矩形波之间任意选择,频率可单独预制,范围为1~9 999 Hz,步进值10 Hz.幅度可单独预置,范围为0.1~7.5 V,步进值100 mV.可产生两路频率相同,相位差可调的正弦波信号,相位差预制范围为o~360.,步进值10产生的矩形波的占空比能在1%~99%预制,步进值1%.图10为本系统产生的低频信号,通道1是产生的三角波信号,通道2是产生的正弦波信号。

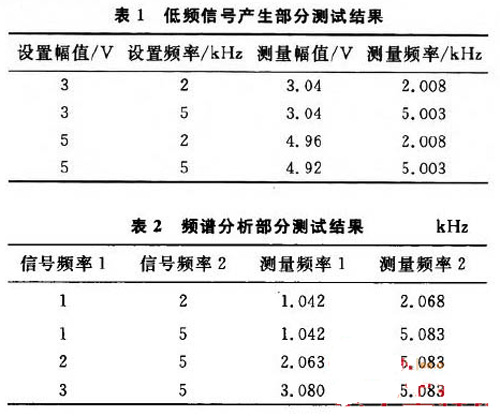

信号叠加电路能对信号发生器输出的两路频率和相位不同的信号进行合成。分析仪部分能对叠加之后的信号进行频域分析,并在显示器上显示叠加信号频谱图。分析仪能分别显示两路原正弦信号的幅度与频率。图11是经过FFT处理过的频谱图。

经过测试,该系统稳定可靠,达到了设计要求。其中低频信号产生部分测试结果如表1所示,频谱分析部分测试结果如表2所示。

6 结论

该双路低频信号发生及分析仪由信号产生模块、信号叠加模块和信号分析模块组成。运用硬件描述语言对FPGA进行设计,在完成了能产生可调幅度频率等参数的双路低频信号频率精度和幅度精度高于一般的DDS集成电路,并有调整矩形波占空比和正弦波相位差的功能。同时实现了对叠加后信号的频谱分析和频率幅度提取,可以直观地观察产生的双路信号叠加后的频谱,并得到相应参数,操作简单,易于实现。可以用作简单的信号产生器,信号叠加器和频谱分析仪。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网