作者:李 旋,刘庆华,廖丁毅

1 内存条的工作原理

DDR内存条是由多颗粒的DDR SDKAM芯片互连组成,DDR SDRAM是双数据率同步动态随机存储器的缩写。DDR SDRAM采用双数据速率接口,也就是在时钟的正沿或负沿都需要对数据进行采样。在本设计中采用的内存是hynix公司的lGB的HYMD564M646CP6-J。内存条的工作原理与单颗粒内存芯片的工作原理一样,主要的控制信号以及控制信号完成的主要功能如表1所示。

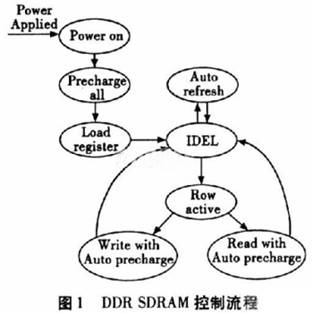

以上的控制信号及地址信号都是由差分时钟信号中CK的正沿触发。DDR SDRAM必须按照一定的工作模式来完成初始化,完成初始化后才能进入到读写过程。DDR SDRAM的控制流程如图1所示。

初始化的过程为:(1)上电后,延时200us等待时钟稳定,然后将CKE拉高,执行一次NOP或者DESELECT操作。(2)执行一次precharge all操作。(3)设置扩展模式寄存器(BAl为低电平BA0为高电平)使能DLL。(4)设置模式寄存器(BAl,BA0均为低电平)复位DLL。(5)执行一次pre-charge all指令。(6)再经过2个自刷新(Auto refresh)指令后再次设置模式寄存器设置操作模式。(7)延时200个周期才能进行读操作。DDR SDRAM的扩展模式寄存器和模式寄存器的定义如图2和图3所示。

完成初始化后进入图1中的IDEL状态,此时可以进行读写操作。在进行写操作时,首先要进入Row active状态,此时选中要操作的bank与row。然后执行NOP操作等待tRCD的时间后可以进入写状态。

2 内存条电路设计

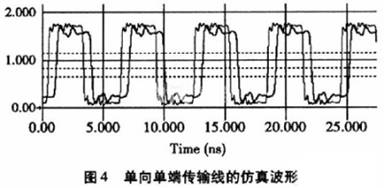

由于DDR SDRAM采用的时钟频率较高,加上DDRSDRAM的数据率为时钟速率的两倍,DDR SDRAM对时钟质量的要求很高,必须保证时钟上升沿的时间小于5%的时钟周期。DDR SDRAM的数据线与相对应的数据采样信号(DQS)的长度要尽量相等,来保证数据的采样窗口尽量要大一些。由于信号质量要求高,我们将所有的信号线都采用微电线和带状线来传输。使用FPGA和内存条的IBIS模型进行仿真来保证设计中信号的完整性,我们将信号分为3类,第一类,由FPGA到DDR SDRAM的时钟差分信号;第二类,由FPGA到DDR SDRAM的控制线;第三类,FPGA与DDR SDRAM之间的双向传输线。对三类IBIS模型的herperlinx仿真如图4:

通过仿真我们可以确定3类信号线中带状线和微带线板厚,铜厚,以及信号线的线宽,线长等参数。

3 FPGA对DDR SDRAM的控制

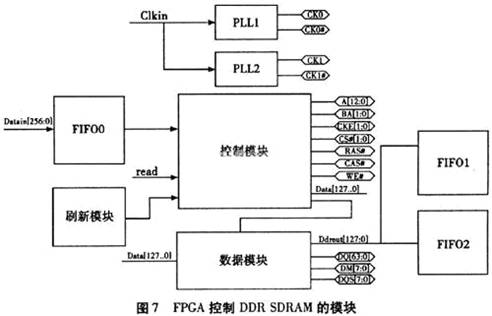

本设计中使用的FPGA是ALTERA公司的cyclone II系列的EP2C20F484C6。对内存条的工作模式设置为BL=4,CL=3,如图7为FPGA对DDR SD-RAM的控制模块框图。

其中,Clkin为外部输入的时钟信号,为了使FPGA到DDR SDRAM的两对时钟信号的质量尽量好,使用FPGA内部的两个锁相环输出差分时钟信号。为了保证锁相环输出的两路差分信号相位一致,在设计PCB时我们使晶振输出到FPGA两个PLL输入的布线距离相等,为了保证两个锁相环输出信号到达DDR SDRAM接口时相位一致,由FPGA锁相环输出到DDR SDRAM的接口布线长度相等。

控制模块采用的工作模式是按照图2所示的状态来跳转,上电以后首先是对DDR SDRAM进行初始化,初始化完成以后就可以进出等待工作的状态。此时刷新计数器开始计数,等待7.8 us后给出刷新请求,在空闲状态时(IDEL)刷新请求的优先级最高,响应刷新请求后执行REFR-ESH指令同时复位刷新计数器。初始化后如果FIF00的读空标志为O说明FIF00中有数据,此时可以进入到写状态。由于采用的是BL=4的工作状态,写操作每次都写入4个64位的数。所以,我们将输入的数据进行并位成256位的数,每次写操作只需要从FIF00中读出一个256位的数。假设我们采用1OOMHz的时钟,每写4个64位的数大概需要10个时钟周期。如果输入的数据位宽为16位,那么由外部传给FPGA的数据率要小于160 MHz。写操作完成的时候进入空闲状态,等待刷新标志或者读空标志。读的时候需要等待系统发出读命令(read),然后进入读状态,读出的数据由Ddrout[127:O]送到FIF01和FIF02中。通过控制FIF01和FIF02的写请求信号来实现将数据分别写入。读的时候BL=4每次读出4个64位数,执行一次读操作大约需要10个时钟周期。如果输出的数据位宽为16位,那么数据由FPGA向外传输的速率要小于160 MHzo控制模块在读写内存条的时候控制数据模块来实现数据率为时钟速度的两倍,数据模块使用两个时钟一个是系统时钟一个是2倍的系统时钟。

因为DDR SDRAM的控制相对复杂,我们可以使用内存条的vefilog模型,通过对内存条的vefilog仿真,我们可以知道自己程序的正确性,图8为modelsim中的仿真波形。如果仿真过程正确,我就可以对程序进行编译,布局布线,然后下载到FPGA中,由于布局布线的延时,输出的信号波形与仿真波形不一致,此时,可以通过调整FPGA内部的锁相环来调整时序,实现对内存条的控制。

4 结束语

通过介绍内存条的工作原理,以及内存条电路设计时的注意事项的介绍,我们可以更合理的实现FPGA与内存条的互连。最后,给出FPGA内部对内存条控制的方法,以及给出仿真波形,实现对内存条的控制。实现FPGA对DDRSDRAM内存条的控制,可以实现大容量高速的数据存储,在工程中的得到广泛的应用。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网