赛灵思继2013年11月初发货业界首款20nm芯片Kintex UltraScale后(http://www.chinaaet.com/article/index.aspx?id=216649),继续积极推动其UltraScale器件的发货进程,于12月10宣布已提供有关Kintex中端和Virtex高端20nm UltraScale系列的详细器件选型表、产品技术文档、设计工具及方法支持。

赛灵思公司全球高级副总裁、亚太区执行总裁汤立人(Vincent Tong)自豪地告诉记者:“赛灵思28nm 7系列产品广泛用于4K电视、OLED、无线等领域;据统计,在2013年前两个季度,赛灵思28nm产品的市场占有率高达72%。”

今年号称是中国4K超高清电视的元年,4G牌照前不久刚刚发放;不断演进的标准,越来越短的上市时间 ,产品差异化的要求,这些都为FPGA的发展提供了广阔的发展前景。

汤立人继续说到:“赛灵思将一改过去单节点、只有FPGA芯片的局面;未来,赛灵思将28nm、20nm、16nm多节点共存,提供FPGA系 列、SoC系列、3D IC系列多种芯片,赛灵思将全面实现All Programmable和Smarter System,瞄准160亿美元的目标市场。”

赛灵思取代ASIC的三大法宝——UltraScale架构、Vivado设计套件和UltraFasta设计方法

在160亿美元的市场规划中,赛灵思一方面要提防老对手,另一方面还需从ASIC/ASSP和嵌入式领域夺取近百亿美元的市场。

取代ASIC/ASSP,赛灵思也喊了好几年,今年的底气尤其足,我想主要得益于三个方面UltraScale架构、Vivado设计套件、UltraFasta设计方法,赛灵思从硅片、工具和设计方法提供了ASIC级的优势。

UltraScale架构是赛灵思在20nm从芯片架构上进行的革新,重新设计的布线架构、类ASIC的时钟和CLB封包技术,使芯片的资源利用率从以前最高的80%提高到90%,大大降低成本和产品开发时间。

Vivado工具已推出一年多,提供全新构建的SoC 增强型、以 IP 和系统为中心的下一代开发环境,以解决系统级集成和生产力瓶颈为目标,在总体生产力、使用简易性和系统级集成能力方面领先一代。ChinaAET甚至还有了Vivado工具的学习视频(http://study.chinaaet.com/course/6100000016 )。

UltraFasta设计方法,这个名词第一次在赛灵思的媒体会上听说,下来查了些资料,请教了专家,终于弄明白了。UltraFasta设计方 法简单地说,就是高效地利用赛灵思的生态系统,在尽可能短的时间内实现FPGA的高效设计,包括IP和设计重用、HLS的软件和硬件设计、生态系统、快速 调试和验证,以达到设计实现和闭合技术、编程和硬件调试方面的最佳实践的集合;有助于制定准确的项目进度和成本的准确估计,把产品开发时间从几个月缩短为 几周,加快产品上市时间,从而增加产品收入。

其实,这些思路赛灵思一直都有,这次提炼成了UltraFasta设计方法。

汤立人指出:“未来FPGA发展,仅有工艺是远远不够的,一定要看工具、架构、生态系统。”赛灵思在设计方法和开发工具上的着力,甚至引起了业内的疑惑,居然有人问“Xilinx是否变成了一家EDA公司? 哈哈

20nm Kintex和Virtex UltraScale的产品路线图

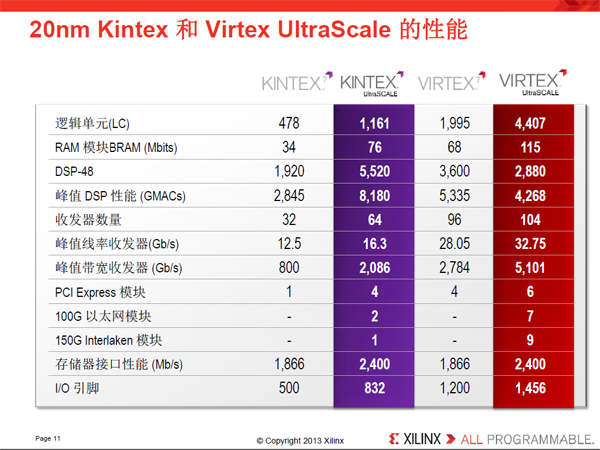

在20nm节点,赛灵思的中端和高端产品系列都将采用UltraScale架构。从下表看出,赛灵思针对不同产品系列在不同的应用下了很大功夫。

就DSP模块,Kintex系列为5520,比Viretex的2880多,是因为Kintex主要应用在无线、雷达领域等,需要更多DSP模块

进行算法方面的应用;对收发器来说,Virtex可用于海量数据中心、400G转发器等,收发器数量和性能明显优于Kintex。

赛灵思此次发布了业内最大容量的XCVU440,采用3DIC封装、第二代堆叠硅片互联(SSI)技术,赛灵思在7系列推出的3D IC——Virtex-7 T2000,集成了4片FPGA Slice,XCVU440只集成了3个FPGA Slice,就具有440万个逻辑单元,为生产和原型设计应用提供了5000万个等效门。据悉,赛灵思在20nm工艺节点上的容量已经超出了此前公开发布 的所有竞争性14/16nm工艺计划。

赛灵思的整个UltraScale系列均采用相同性能的逻辑架构和关键架构模块,打造出了最佳可扩展的架构。此外,赛灵思系列产品间引脚兼 容,Kintex UltraScale FPGA可向Virtex UltraScale平滑移植。规划中的目标市场如下图。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网