引言

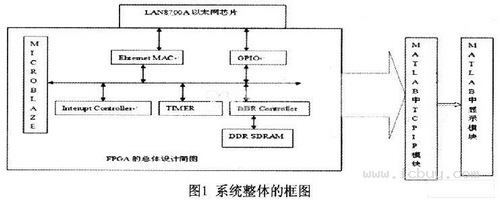

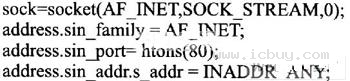

近年来,随着信息技术的发展,网络化日加普遍,以太网被广泛应用到各个领域。例如在数据采集领域,一些小型监测设备需要增加网络实现远程数据传输的功能,只要那些设备上增加一个网络接口并实现了TCP/IP协议,就可以方便地接入到现有的网络中,完成远程传输数据的相关功能,所以小型设备的网络技术一直是大家关注的焦点。另一方面,随着单片FPGA的逻辑门数不断增大,人们开始考虑将整个嵌入式系统集成到单片FPGA来实现,于是2001年Altera第一次提出了可编程片上系统(SOPC)概念,并且推出了第一款嵌入式处理器软核Nios以及之后的第二代NiosII以及相应的开发环境,此后Xilinx也推出了MicroBlaze微处理器软核,之后,随着Altera的CycloneIII和StraTIxIV以及Xilinx的Spartan6和Virtex6等一系列大容量FPGA的推出,Xilinx于2009年正式提出了目标平台设计并且推出了相应的软件ISE11,至此,嵌入式系统真正开始走向了片上系统,自然,这中间也包括了以太网的嵌入式片上系统。 Matlab是美国MathWorks公司提供的商业数学仿真软件,其中Simulink是Matlab中的一种可视化仿真工具,是一种基于框图的设计环境,可以实现数据的仿真和处理,它提供了一种快速、直接明了的方式,用户可以实时看到系统的仿真结果并且进行相应的数据处理。基于以上事实,本文提出了基于FPGA的嵌入式以太网与Matlab通信系统的设计和研究,采用Xilinx公司的MicroBlaze嵌入式微处理器软核,利用它和相应外设IP核一起完成SOPC的设计并且完成与Simulink数据的传输,最后动态显示以太网传输的数据。 系统硬件平台设计 1、系统总体硬件的结构 在系统硬件结构中,考虑到系统复杂度和成本因素,我们选用了Xilinx公司的Spatan3A系列的XC3S700A作为主控制芯片,该芯片为Xilinx的Spartan系列的低端FPGA,采用了65nm技术,在集成度和性价比上都要优于先前Spartan系列的FPGA,系统外挂一块Micron公司的32M×16bits的DDR2芯片MT47H32M16作为外扩SDRAM,以及一片Numonyx公司的16Mb的SPIFlashM25P16作为数据存储器,而10/100Mb以太网我们采用单片PHY芯片加Xilinx的MAC软核来实现。该方案将物理层和MAC分开,将MAC用IP来实现,从而整个系统更加灵活。其中单片PHY芯片有BroADCom公司的BCM5221,Intel公司的LXT971A、LXT972A,SMSC公司的DM9000、LAN83C185等。这里我们采用SMSC公司的LAN83C185来实现物理层。 2、系统整体框图 虽然Matlab中可以采用相关命令创建一个TCP/IP的模块进行数据的接收和显示,但是与Simulink中TC/IP模块相比较为繁锁,因此选择用后者动态实时显示从以太网发送过来的数据,并可进行相应的处理。本设计主要是完成发送正弦函数数据并在Simulink的接收模块中显示正弦函数图形。系统的整体的框图如图l所示: MicroBlaze的系统硬件配置和Simulink接收块的搭建 1、MicroBlaze和系统设计 Xilinx公司的MicroBlaze嵌入式软核是业界优秀的32位软处理器IP核之一,它支持CroConnect总线标准设计集合,具有兼容性和重复利用性,最精简的核只需要400个左右的Slice,MicroBlaze软核内部采用哈佛结构的32位指令和数据总线,便于各个外设和它们之间的信号传输及相应的控制,它有下面的几种互联总线: (1)处理器本地总线(PLB)。可以将多个PLB主设备和PLB从设备连接到整个的PLB系统中。 (2)高速的本地存储器总线(LMB)。用来取RAM块的同步总线。 (3)XCL总线。是一个高性能的外部内存访问总线。 (4)FSL总线。用于点对点的单向通信总线。 使整个系统的软硬件设计,包括系统硬件平台的搭建,驱动程序的配置,Xilkernel操作系统内的核参数配置,软件库的设置,文件系统的生成及外设控制芯片接口配置都可以在EDK(EmbeddedDevelopmentKit)内完成。EDK的整体开发流程如图2所示。 整个系统设计具体操作如下: (1)在EDK的集成开发环境XPS(XilinxPlatform.Studio)中,处理器功能单元,系统外围总线结构,终端外设以及相应的地址映射和默认的驱动等都可以在BSB(BaseSystemBuilder)中完成。在Microblaze系统的基本构建中其主要设置如下:使用SingleProcessorSystem系统,LocalMemory为16k,系统时钟频率为62.5MHz,定时器和以太网中断必须连接到处理器的中断控制器上,另外,本设计还用到的GIOP、EthernetMAC、DDR、SDRAM控制器等,其间用到的IP驱动,都是用xilinx提供IP的自带默认的相应驱动。 (2)最后XPS自动生成微处理器硬件规范MHS(MicroprocessorHardwareSpecificaTIon)和描述软件系统结构的微处理器软件规范MSS(Micro-processorSoftwareSpecification)文件以及一些相关的文件。这些文件都可以手动进行修改,从而是使整个系统更加的优化。 (3)生成的系统最后生成bit文件,把其文件下载到目标板子上。 2、Simulink接收模块的搭建 Simulink中TCP/IP中的接收模块,其终端的地址,端口的设置要与FPGA上的以太网的IP地址、端口的设置一致,这就为TCP/IP接收模块指定了要通信的地址即完成了接收模块TCP/IP的相关配置,也就完成了FPGA与Matlab中以太网通信的接收模块的搭建,在Simulink中,具体的模块设计如图3所示。 通信数据通过此模块可以较直观地用图形动态显示。 系统的软件平台及网络协议的实现 1、软件内核和协议 本设计主要选择了Xilinx公司的精简嵌入式操作系统Xilkemel,它是Xilinx提供的用于EDK系统的小型、模块化的嵌入式操作系统内核,它支持Microblaze核,与EDK形成的硬件系统无缝连接,具有可定制、CPU资源占用较小、运行速度快等特点,是MicroBlaze嵌入式软核的理想操作系统,其整体的开发流程如图4所示。 网络通讯协议我们采用TCP/IP协议,该通讯协议采用四层(应用层、传输层、互连网络层、网络接口层)层级结构,每一层都呼叫它的下一层所提供的网络来完成自己的需求,系统分为两部分实现: 第一部分为物理层和MAC层,本设计中用LAN83C185来实现物理层,MAC层由Xilinx公司的EthernetMACIP核,并作为整个MicroBlaze系统硬件的一部分在FPGA内实现。 第二部分是运输层和网际层,主要由软件代码实现。TCP/IP网络通信软件允许用户远程注册到另一个系统中,并从一个系统复制文件到另一个系统,虽然Xilkernel本身不带有文件处理系统和TCP/IP协议栈,但它与Xilinx公司的LwIP库具有良好的接口,加上系统支持库LibXilMFS可形成一个比较完整的嵌入式系统,其特点是内核配置功能都已集成到EDK工具中,使用简单、方便,内核启动静态创建线程,而动态分配内存,可加载或卸载不同功能模块来实现内核的高扩展性。 本设计主要采用LwIP3.OOb(LightweightInternetProtocolstack)协议模块套用于嵌入式系统的开放源代码TCP/IP协议栈中,LwI-P3.00b提供二种API模式:Socket模式和RWA模式,由于Socket模式开发难度不大,只要启动Xemacifinputthread线程,从中断响应的过程中接收数据包并转移到LwlP的tepipthread中就可以。所以基于方便考虑我们决定上层协议部分协议模块采用Socket模式,因此需在MSS文件里对LwIP进行例化(包括相应的LwIP参数设置)从而减少存储器利用量和代码编写。 2、网络通信程序的实现与设计 网络通信程序主要完成从超极终端发送数据,传到Simulink中的ICP/IP接收模块。下面是主要的网络通信程序: Server_thread()函数是Xilkernel的第一个线程,初始化LwIP协议栈。 ServerAppThread()函数可完成MAC、IP、掩码以及网关的配置,并完成Socket应用。 以太网的配置如下: 当服务器程序开始运行时,主进程就创建一个套接字, 并通过bind函数绑定,用函数listen进行*,之后用lwip_accept进行接收,然后用sys_thread_new启动进程,processGet和ProcessCommand函数分析数据包的内容并应用webserber定义的相关的命令实现相关的应用,write函数实现数据的发送,完成Socket服务并把数据发送给客户端。 Simulink中用TCP/IP模块,remoteaddress参数设定为(211、80、192、237),端口设定为80,即与IP4_ADDR(&ipaddr,211,80,l92,237)和address.sinport="htons"(80)设为一致,这样就保证了接收与发送网络地址和端口的一致性,保证数据传输的可实现性。设计发送的数据为:t=0:0.25:10,Y=sin(2*pi/10*t),数据列表如下: 对应的Simulink接收模块的数据图形显示如图5所示。 由图5我们可以看出,接收到的数据和发送的数据基本一致。 结论 本文研究了TCP/IP通信协议在Xilinx公司FPGA上的实现,介绍了其软硬件的系统组成及原理,通过建立一个例子加以说明和应用这个设计平台,证明了此平台设计可行性,并且完成了FPGA与Matlab的通信,为数据的实时显示及实时控制提供了很好的平台和设计方法,本设计也完成了CPU软核设计的实现,其功能可根据需要进行定制,非常灵活,不但引入了软核处理器和嵌入式操作系统Xilkernel,而且应用了Lw-IP_300b栈,使用大量的IP核,这样大大降低了系统平台的复杂度,缩短了开发的周期,其软硬件部分的设计分离的设计架构,使得整个系统修改和重构更加方便,真正实现了所谓的片上系统。而本设计采用Matlab接收数据,并且可利用其强大的数据采集、处理、仿真、实时动态显示的功能来更好完成数据分析研究。

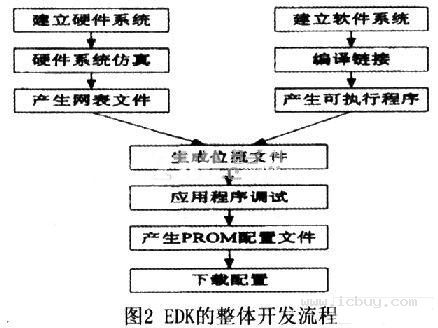

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

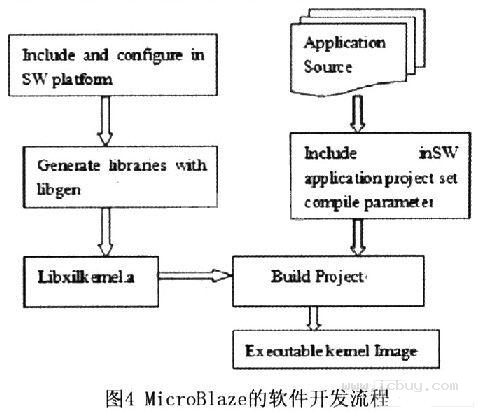

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

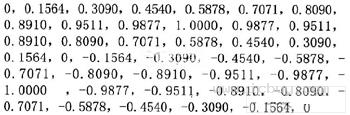

@2003-2020 中国电子顶级开发网