为了帮助客户进一步提高生产力,成功实现新一代创新技术,赛灵思针对其屡获殊荣的 Vivado?设计套件推出了 UltraFast ?设计方法,帮助使用 Vivado 的设计团队加快在赛灵思 28nm 7 系列器件以及即将推出的20nm/16nm UtraScale ?产品系列上成功实现设计。

Vivado 设计套件的高级产品市场总监 Ramine Roane 指出,这款新的设计方法并不是完全另立门户,而是公司根据业界专家的提议精选了数项最佳实例并将其精简为一套有效方法,以推动设计团队走向可预测的成功,该方法统称为 UltraFast 设计方法。这些最佳实例涵盖开发板规划、设计创建、设计实现与收敛、编程和硬件调试等各个方面。

Roane 指出:“UltraFast 设计方法将帮助设计团队充分利用 Vivado 设计套件和赛灵思 All Programmable 器件的先进技术,以提高生产力,并不断缩短设计时间,准确预测设计进度,进而加速产品上市进程。”UltraFast 设计方法的推出是赛灵思如何保持领先于竞争对手整整一代水平的又一例证。赛灵思不仅推出最佳器件和最先进的工具套件,而且还提供了业界最全面的设计方法。

为了加速推广 UtraFast 设计方法,赛灵思发行了免费的设计方法手册《Vivado 设计套件的 UltraFast 设计方法指南》(

UG949),帮助读者一步步了解设计方法,包括开发板的选择、RTL 设计乃至实现和最终调试等。该手册提供了全面的检查清单(checklist),引导工程师完成整个设计流程。此外,Vivado Design Suite 2013.3 版本还将设计方法的许多元素实现了自动化(包括 linting),并添加了新的设计规则检查 (DRC rule decks),题为“Methodology”和“Timing”。新版 Vivado 设计套件还提供硬件描述语言 (HDL) 和赛灵思设计约束 (XDC) 模板,有助于优化综合和实现的结果质量 (QoR)。赛灵思还提供一系列免费的在线自学视频,并在全球不同地区提供官方培训课程。

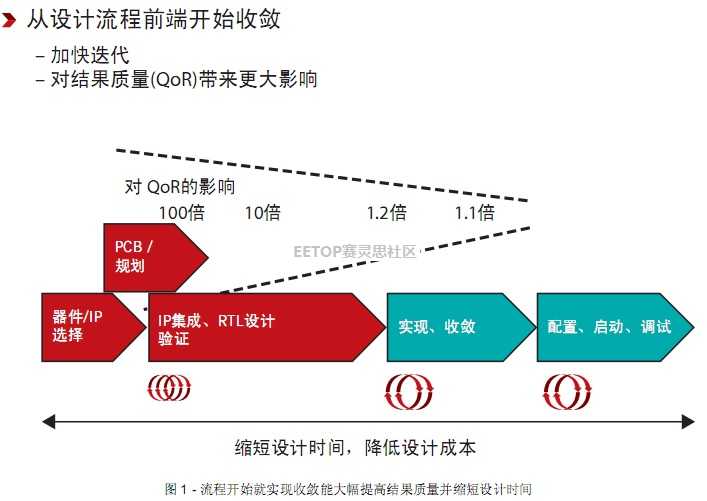

加速收敛的设计方法Roane 指出,UltraFast 设计方法的主旨就是把设计收敛提到设计流程的前端,也是 QoR 影响较大的地方(见图 1)。这样,设计团队就能快速组建出一个“设计期正确”(correct-by-construction)的设计方案上。 Roane说:“如果能在设计流程早期阶段全面了解情况并做出决策,就能有效避免实现阶段耗时过长。”

可编程行业唯一一款在流程的每个环节(从设计输入到IP集成、RTL综合、实现(优化、布局、物理优化、布线)乃至启动)均支持交互设计分析和源文件交叉探测的设计套件。Roane说:“采用传统工具时设计者只有到设计流程结束时、在规划全面实现后才能发现问题,如果设计方案不能达到预期效果,唯一的办法就是从头再来,而且根本不清楚问题的原因,不得不进行多次长时间迭代循环。”

实现交叉探测和分析功能的主要因素在于 Vivado 设计套件的统一数据模型。Roane 说:“统一数据模型使设计团队能够在整个流程中采用相同的分析和收敛程序。这相对于老式设计套件而言是一大优势,能帮助工程师在多个环节上(甚至在尚未保存设计修改的临时记忆中)修改设计方案,通过交叉探测到源文件或者其他设计视图。赛灵思设计的这款统一数据模型能扩展运用到包含数百万个逻辑单元的高端器件,而同类竞争工具刚刚开始满足中端器件的要求。”

或许,能反映 UltraFast 设计方法加快设计收敛的最好例证就是“基线Baselining)”概念。

通过Baselining 快速时序收敛“基线 (Baselining) 是一种用于加速设计收敛的技术,它着重于解决内部Fmax,这是最大问题,10 次有 9 次收敛所出现的问题就是它。这能避免由于复杂的、极易出错的 I/O 约束和时序特例而耽误时间,防止用户和工具被引导至错误的方向。采用基线技术,设计团队能用最简单的约束启动收敛进程,集中精力于触发器路径。随后,根据问题是出在时钟路径或数据路径上,还是连线延迟或逻辑延迟,我们可采取有文档记录的修改措施,并重新运行分析。”

一旦设计团队用基线 XDC 收敛了时序,就基本完工。随后就需要添加I/O接口约束。Roane指出:“必须确保这些约束的正确性,这样才能避免出现‘假的’时序问题。”

“正由于此,我们为源同步,中间对齐的 DDR I/O 约束等提供 XDC模板。如果需要,我们可用时序特例来微调约束,或者进行一定的布局规划。不过重要的是应当记住,如果相应路径不是关键路径,那最好不要采用时序特例。同样,设计过度布局规划造成的问题远比带来的作用要多。”Roane 指出,基线法并不能替代签署约束(sign-off constraint):“仍然要在完备的约束的基础上验证设计方案。”UltraFast 设计方法还给出了获得原始签署约束的详细步骤。Vivado 通过大量批处理和图形界面程序使这一任务自动化,分析时序路径、时钟网络、时钟之间的交互等。新的时序 DRC 规则也可用于检查设计的约束及时钟网络。