流视频、社交网络和云计算等新兴 Web 应用亟需能容纳数千台服务器的仓库规模的数据中心。在数据中心和其它计算机集群中,用于处理大数据集的主要编程框架之一即为 MapReduce 框架 [1]。MapReduce 是一种运用大量节点来处理大数据集的编程模型。用户负责设定“Map”和“Reduce”功能,然后由 MapReduce 调度器将任务分配给处理器。

MapReduce框架的主要优势之一在于,其能托管在由不同类型处理器构成的多个异构集群中。大部分数据中心都纷纷采用高性能的通用型器件,如英特尔至强 (Intel Xeon)、AMD 皓龙(AMD Opteron)和 IBM Power 处理器等。但是,即使在应用不属于高计算密集型而属于高I/O密集型的时候,这些处理器也会消耗大量的电力。

为了降低数据中心的功耗,微服务器作为一种替代性平台近期倍受关注。这类低成本服务器通常采用嵌入式系统中使用的低功耗处理器,如ARM处理器等。微服务器主要针对轻量级或并行应用,处理此类应用最行之有效的方法是使用在节点间拥有充足 I/O(而非拥有高性能处理器)的单个服务器。微服务器方案具有众多优势,如可减少购置成本、缩小占用面积,并能降低特定应用类型的功耗。

在过去的几年里,SeaMicro 和Calxeda 等几家厂商已开发出基于嵌入式处理器的微服务器。但是,MapReduce 框架会占用嵌入式处理器的多种资源,从而会降低运行在这些平台上的云计算应用的总体性能。

为了克服这个问题,我们的团队已为 MapReduce 框架开发出一种能在全面可编程平台上与 ARM IP 核实现高效整合的硬件加速单元。为了开发并评估所提议的方案,我们选用了开发板上集成有双核 Cortex-A9处理器的赛灵思

Zynq-7000 All Programmable SoC。

MapReduce 硬件加速器单元MapReduce 加速单元负责处理Reduce 任务的高效实现。其主要工作是合并来自各个处理器的中间键 / 值对,并为插入新键和更新(累计)键 / 值对提供快速途径。我们将MapReduce 加速器作为协处理器来实现,可通过共享总线作为多核处理器的扩充。图 1 为多核 SoC 中加速器方框图。

图1 - MapReduce 硬件加速器的方框图

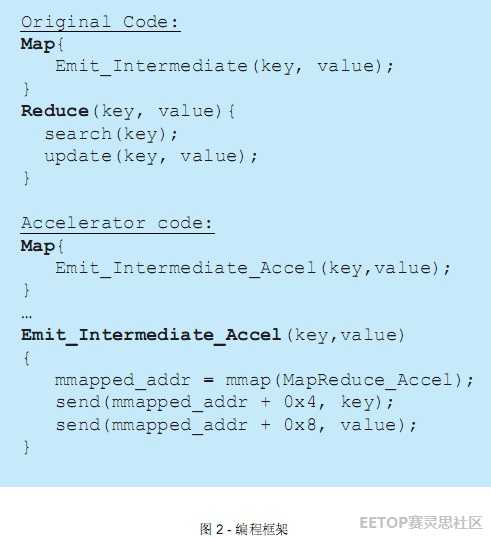

编程框架

图 2 为使用硬件加速器的 MapReduce应用编程框架。在原始代码中,Map级发射键 / 值对,而 Reduce 级则搜索该键并消耗若干 CPU 时钟周期的时间来更新(累加)新值。使用 MapReduce 加速器的情况则与此相反,Map 级仅发射键 / 值对,而MapReduce 加速器则合并所有的键 /值对并更新相关条目,因而无需采用Reduce 功能。