用Zynq SoC 实现 Red Pitaya 开源仪器

发布者:jackzhang

时间:2014-01-17 13:51:13

作者:

Aleˇs Bardorfer,理学博士

Red Pitaya LLC 公司

ales.bardorfer@redpitaya.com

Matej Oblak

在读理学硕士

Instrumentation Technologies, d.d. 公司

matej.oblak@i-tech.si

Borut Baricˇevicˇ

Red Pitaya LLC 公司

borut.baricevic@redpitaya.com

Rok Urˇsicˇ

Red Pitaya LLC 公司

rok.ursic@redpitaya.com

在电子工业的早期,示波器、信号发生器等测试测量设备功能固定,只能执行少量明确的任务。过去数十年里,制造商运用 DSP的可编程功能为特定应用量身定制了较丰富的功能集。但只有制造商在产品出厂之前才能为这些仪器编程并确定其最终的功能集。

虽然现今市场上大多数仪器具有较丰富的功能集,但并不能满足客户特定项目所需的精确功能,这对世界各地科研机构和大专院校中那些致力于用仪器等较小型子系统构建大型复杂系统的跨学科研究小组而言尤为如此。在科研工作中,往往需要比厂商设计提供的功能更精细的设备。一般来说,高速反馈系统涉及两个(或多个)需要极低抖动、硬实时响应的仪器子系统,通常会出现集成方面的问题。

往往仪器的接口难以实现所需的总体集成系统性能。封闭源码且面向 DSP的仪器不允许此类集成。

Instrumentation Technologies 公司的工程师一直想知道,如果开发出一种用户可编程、用户可定制的开源仪器(或信号处理平台)会怎样?为此,我们开发出一块得到开源开发生态系统支持的“Red Pitaya”小型测试板。Red Pitaya 系统有望通过单个可重配置的器件,以明显低得多的价格,取代众多标准测试测量仪器。图1 为 Red Pitaya 的系统架构图。这是一款具有多个模拟 / 数字输入输出的新型仪器(信号处理系统)。

图1 - Red Pitaya 系统架构

系统架构理想的仪器一般要求在模拟域和数字域表现出卓越的性能。频率日益提高的模拟域仍然对仪器的本底噪声和测量性能有着严格的要求。而数字域由于稳定性好、抗噪能力强、时不变性、能够执行高度复杂的处理且能够与标准连接功能相结合,正蓄势待发。因此信号处理正日渐从模拟域向数字域过渡。

新型信号处理系统的基本方法是在模拟前端尽量采用通用电子设备,在处理链上尽量采用高速 ADC 进行信号采样。数字侧倾向于先处理信号,然后尽可能晚地将它们发送到处理链中的 DAC。模拟后端也尽量采用通用电子设备。采用这种架构,处理 / 测量系统的所有特性都集中在数字域,模拟电子技术保持简单、通用。这种以数字为主的新型架构为通过硬件定制执行多个应用领域内的一系列任务提供了契机,可能仅受模拟前端后端的带宽和数字域的计算资源(主要是FPGA 和 CPU资源)的限制。

从速度的角度来看,Red Pitaya上主要有两类处理链。一类处理链是利用

FPGA 的极高速度、极低抖动硬实时处理功能实现的、带宽约为50MHz 的信号处理链;另一类处理链是通过 CPU 实现的,可能用于运行硬实时操作系统的带宽约为 50KHz 的信号处理链。

根据我们的经验,在可重配置仪

器中将 FPGA 和 CPU 当作信号处理系统的基本模块,一直是一种成功的组合方式。这种组合为高性能 FPGA和易于编程的 CPU 之间的信号处理部分分区提供了很大的自由度。特别是几乎所有仪器都面临着从原始采样点到仪器输出点减少大量输入数据的难题。例如一幅示波器图只需要保持1,000 个点。

典型的测试结果示例包括示波器的信号图、频率分析仪的频域图或通过处理吊顶摄像头输出得到的篮球运动员位置坐标轨迹图等。所有这些测量输出所代表的数据均远少于仪器的原始信号输入数据。输入数据是在极高频率下采样得到的。从仪器的输入到处理结果输出这个过程中的数据减少就是嵌入在仪器中的数字信号处理功能的主要工作。

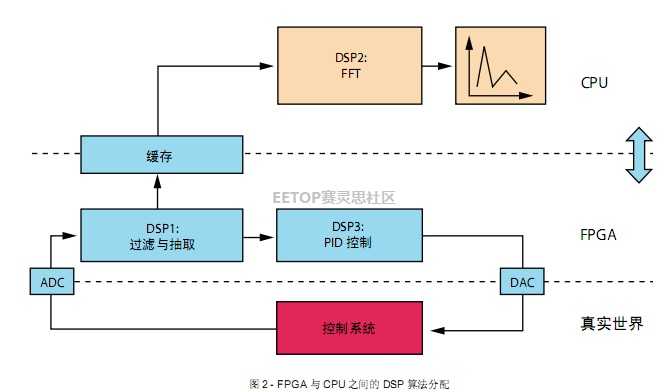

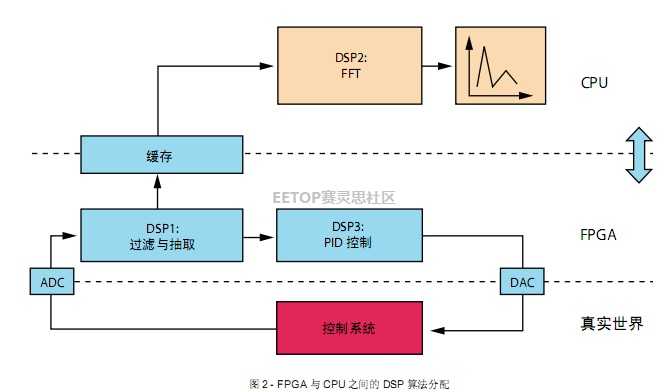

把 FPGA 和 CPU 同时嵌入在信号处理系统中,使开发人员能够自由决定如何在 FPGA 和 CPU 之间分配 DSP 处理任务。就处理的适用性来说,这两者之间稍有区别,但两种都能够完成数字信号处理。一般来说 FPGA 适合处理超高速但简单的DSP 运算,但不太适合复杂的程序运算 (procedural operations)。而 CPU则擅长处理速度较慢较为复杂的程序运算。此外,CPU 还擅长于运行诸如 Web 服务器等标准交互接口。虽然FPGA 开发工具近年来有大幅改进,一般而言与 FPGA 中的 RTL 编码和数字结构综合相比,编写运行于 CPU 上的程序软件依然相对简单。

FPGA 与 CPU 之间的 DSP 处理自由分配还能带来另一大优势,即能够快速对性能有限但功能齐全的系统进行原型设计。在 CPU 上执行大部分DSP 处理工作,不仅可以在项目开发早期阶段进行原型演示,适用于市场营销目的,同时在项目开发后期阶段,使用这种方法可以把 DSP 的关键性能部分平滑移植到 FPGA 上,打造出功能相同但性能完备的最终产品。

图 2 就是在 FPGA 和 CPU 之间分配DSP算法的实例。在开发过程中,FPGA和CPU间的分区界限可以变化。由于 DSP 处理被分割开,部分处理过的数据必须在 FPGA 和 CPU 之间来回传输。因此,两者间的总线速度极为重要,以防止造成额外的处理时延。

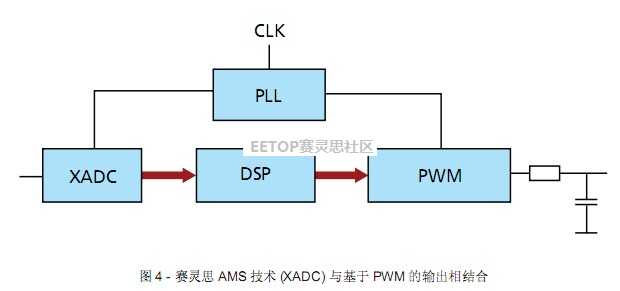

Red Pitaya如图 3 所示的 Red Pitaya 系统在赛灵思 Zynq®-7010 All Programmable SoC 基础上构建而成。Red Pitaya 拥有高速双通道 125Msps 的信号采集和信号生成能力,与位于其间的 FPGA DSP 处理功能相结合,即构成硬实时反馈环路。除了高速信号处理功能,该系统还拥有数个速度较慢(约100KHz)、采用赛灵思模拟混合信号(AMS) 技术(图 4)的 I/O通道和多个数字 I/O。如果用户使用高速串行菊花链连接器将多个 Red Pitaya 模块以菊

花链方式连接起来,就能够实现分布式处理。采用这种方法,用户就可以通过将多个 Red Pitaya 子系统互连,构建出具有更多输入输出端口的复杂系统。CPU 负责运行 Linux 操作系统,并为 1000Base-T 以太网、USB OTG、Micro SD 存储和 USB 串行控制台提供支持。

图3 - 通用Red Pitaya 仪器平台

Red Pitaya 仪器的初始应用包括双通道125Msps示波器、频谱分析仪、信号处理器和 PID 控制器等。Red Pitaya 仪器及配套的应用程序和生态系统将于 2013 年 12 月推出。其开放源码性的魅力在于爱好者可以根据自己特定的需求开发出定制应用。和任何开放源码定制的情况一样,其他人也有机会使用改进的或全新的仪器或应用。预计 Red Pitaya 生态系统将不断发展和完善更多其他应用。