验证RTL模块或FPGA是否满足要求可能颇具挑战。但有些方法可用来优化验证流程,以确保验证成功。

验证FPGA或RTL模块可能是一个非常耗时的过程,因为工程师要极力确保设计能够按照规范要求并在可能导致模块错误的极端状况下正确运行。工程师 通常采用测试平台来达到验证目的,测试平台是一种为测试设计而创建的文件。然而,测试平台可简可繁。下面,就让我们来了解一下如何充分利用测试平台,而又 不会使其过于繁琐。

什么是验证?

验证是指确保被测单元(UUT)同时满足设计要求和设计规范,适合其预期目的。很多情况下是由独立于设计团队之外的团队来执行验证工作,对项目有个全新的认识。这样,设计UUT的人并非是断定其能否正确工作的人。

鉴于现代FPGA设计的尺寸之大、复杂程度之高,要确保UUT按规范运行可能是一项艰巨的任务。因此,工程设计团队必须在项目初期确定采用哪种验证策略。选择策略技巧如下:

. 仅功能仿真——该技术检查设计是否正确运行。

. 功能仿真和代码覆盖率——该方法在检查功能正确性的同时,还要检查设计中所有代码是否都经过测试。

. 门级仿真——该技术同样验证设计的功能性。当用来自最终实现的设计的时序信息进行后端注释时,执行这种仿真方法会耗费大量的时间。

. 静态时序分析——该方法对最终设计进行分析,以确保模块达到时序性能。

. 形式等效校验——工程师使用该技术检查网表与RTL文件的等效性。

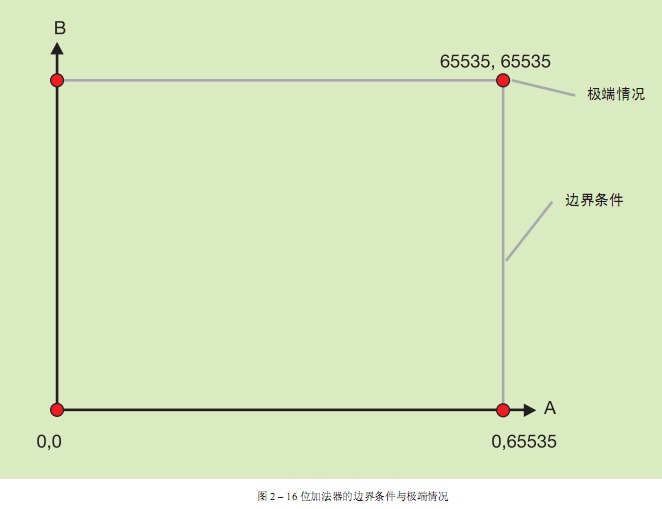

边界条件是指输入中有一个达到极值,而极端情况是指所有输入均达到极值。

无论使用哪种验证策略,工程设计团队都需要制定一个测试计划,规定如何对每个模块和最终FPGA进行验证并满足所有要求。

自检测试平台

为激励UUT而创建的测试平台既可以是自检式也可以是非自检式。如果您倾向于使用非自检式,那么需要用肉眼观察电脑显示器上的测试结果,以确定测试平台能

够按预期工作。而自检式测试平台与传统测试平台的区别在于,除了施加激励外,还要依照预期结果对UUT的输出进行检查,如图1所示。这样就可以明确地说明

UUT是否通过测试。将该功能与通过文本文件的控制与汇报功能相结合,就能创建一种功能非常强大的验证工具。

自检测试平台具有多种优势。首先,用肉眼验证仿真波形的这种方法非常耗时而且极其复杂,而自检测试平台则能为您省去这种人力成本。此外,自检测试平 台还能提供综合而全面的通过或是失败报告,您可在后续的设计流程中将其作为测试凭证保存并使用。若UUT需要在后续阶段进行设计迭代,那么返回测试平台并 确定测试是否通过或失败(该流程通常称为回归测试流程)所需的时间就会远远少于采用传统测试平台所耗费的时间。

极端条件、边界条件和应力测试

使用测试平台的目的是确保模块按照功能要求执行,任何极端状况都能得到解决,同时,最重要的是测试平台应充分执行UUT代码。因此在验证设计模块时,经常

用到“玻璃盒”测试法,因为这样可以了解和观察UUT模块的内部情况。相比之下,当UUT为FPGA时,由于顶层需要更长的验证与仿真时间,您需要使用顶

层的黑盒测试法。

为了根据要求验证设计的功能性,测试平台所应用的激励必须与模块预期在运行中能看到的激励相同。然而,测试所有可能的输入以证明功能合规性可能是一个非常耗时的过程。因此,工程师会将重点集中在边界条件和极端情况上,并测试一些典型操作值。

边界条件是指输入中有一个达到极值,而极端情况是指所有输入均达到极值。能较好体现这两种情况的实例是简单的16位加法器,用于累加两个数值并得出结果。图2给出了这种情况下的边界条件和极端情况。

您可以清楚地看到,极端情况是当A和B输入都等于0;当A等于0,B等于65535;当A和B都等于65535;以及当A等于65535,B等于0。边界条件是极端情况之间的值。

对于有些应用,可能要对UUT进行应力测试,以确保在正常运行之外有一定的裕量。应力测试会根据模块而变化,但可能涉及重复操作,从而使缓冲器和FIFO溢出。对设计采取应力测试可减少验证工程师损坏UUT的几率。

代码覆盖率

验证团队还需要一个指标来确保测试平台已正确执行UUT。该指标通常通过使用代码覆盖率来提供,以确保UUT被正确执行。对于代码覆盖率问题,下面给出了一系列需要考虑的参数。

. 检查每个可执行语句,以确定执行次数。

. 执行所有IF、CASE和SELECT的可能分支。

. 测试代码分支内的条件和子条件,以查看是什么条件导致此分支为真。

. 遍历通过HDL的所有路径,以识别未经过的路径。

. 监控VHDL过程敏感列表中的信号以及等待语句,以确保所有触发条件都经过测试。

100%满足上述参数并不能证明UUT满足功能要求。不过,这样能轻易识别出哪段UUT未被测试平台执行。这里需要重点提一下代码覆盖率只解决了UUT内部问题。

测试函数与程序

验证团队应为经常使用的测试例程建立一个库,使团队中的所有成员都可针对该项目甚至其它项目使用该库。建立该库不仅能加速开发,而且还能从测试平台中得到标准化输出。这种标准化输出有助于模块的分析与验证。

您可以将这些标准函数和程序运用于众多应用中。一些常用方法为:

. 激励生成器:例如,用来测试复位应用程序和释放,或驱动通信接口的标准方法

. 输出检查:依照预期结果检查输出结果,并通过副本或文件进行报告

. 模型:器件的标准化模型,在运行过程中将与FPGA或模块实现接口相连

. 日志函数:用于显示结果的标准化报告格式,可简化分析。日志功能还提供设计要求的验证证明,用以表明合规性。

良好的输出检查函数可利用VHDL信号属性“stable”、“delayed”、“last_value and”和“last_event”。这些属性在确认UUT能否与用于存储器的时序接口或其它接口兼容时非常重要。这些函数还能用来确保UUT达到“设置 -保持”时间,并可在未达到时发出错误报告。

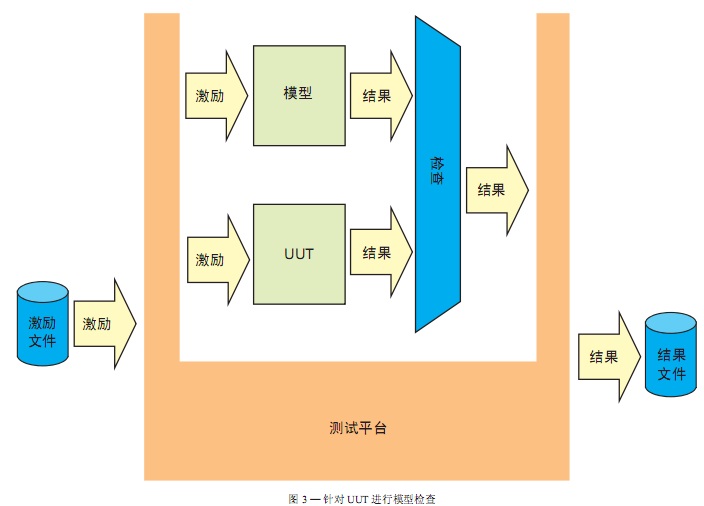

行为模型

有时候您可以参照不可综合的行为模型验证UUT的性能,该模型执行的是与UUT相同的函数(见图3)。该模型与UUT都采用来自测试平台的相同激励,且对

两个模块的输出进行逐周期对比,以确保它们的行为方式相同。模型或测试平台可能需要考虑UUT的时延问题,以便对正确结果进行比较。

使用 TEXTIO文件

如果您使用VHDL来验证设计,那么可以利用TextIO程序包从文本文件中读入激励矢量,并在结果文本文件中记录包括通过或失败在内的结果。验证工程团

队随后便可创建一些用来检测UUT的激励测试文件。这种方案很有效,因为改变激励可变得与更新文本文件一样简单。如此便能实现简单而快速的更新,同时对可

能在实验室或最终硬件中引起问题的情况进行测试。

在VHDL中,STD测试程序包支持与文本文件的交互,而且如果仿真器支持VHDL 2008,还允许使用std_logic和std_logic_矢量。如果您的仿真器不支持VHDL 2008,那么您始终可以利用非标准但很常用的std_logic_textio程序包来提供相同的支持。Verilog可提供用以读取和写入文本文件的 同类工具。

验证设计比创建可实现的设计更加艰巨。在项目生命周期早期阶段仔细斟酌验证策略,团队方能准备好必要的测试计划和基础设备,全力支持这一关键流程。

我们还需要考虑什么?

测试平台应具备时间无关性,这意味着测试平台既可测试RTL也能测试行为UUT以及后端注释有SDF时序信息的后布局布线网表。尽管门级仿真会因分辨率的原因而占用大量时间,但有时这样做是必要的。

验证团队还应考虑使用Tcl脚本对正在执行测试的仿真工具进行控制。这种方案能支持可重复性更高的流程,因为在GUI中设定的所有选项以及仿真运行 之间的变化都能在用来控制仿真的Tcl文件中加以定义。此外,这些文件还能实现自我编制,从而减少UUT验证所需的文档编制工作。

计划与基础设备

验证设计往往比创建可实现的设计更加艰巨。在项目生命周期早期阶段仔细斟酌设计验证策略,团队方能准备好必要的测试计划和设备,全力支持这一关键流程。考虑以上几点有助于建立合适的测试平台,灵活完成当前的任务。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网