摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方法,接收模块在收到外部发送的并行数据时,通过直接查找映射的方法转换成利于传输的串行信号。串行信号经串并行转换模块,将数据经10B/8B解码模块解码还原成原始数据。为了更好实现数据的传输,系统加入了极性偏差RD控制。结果表明,该8B/10B编解码系统设计方案传输数据稳定,满足设计要求。

关键词:串行数据传输;8B/lOB编解码;极性偏差(RD);VHDL

随着通信技术的发展,在复杂的电磁环境下正确传输数据受到人们的关注,因此性能优异的光纤通讯越来越受到青睐,而误码率要满足设计需求,关键在于串行传输数据所选用的编码方法。

8B/10B编解码技术是主流传输标准的编解码技术之一,广泛应用于高速串行标准中,例如光纤通道1、PCI-Express、串行ATA、1394b等。8B/10B编解码技术设定传输数据流拥有连续“l”或连续“0”不能超过5个,保证传输的直流成分接近0,基线漂移减至最小,避免因接收端时钟漂移或同步丢失而引起数据丢失。8B/10B编码方法具有DC补偿功能,能够保证链路中不随着时间推移而出现DC偏移。这使得信号的转换不会因电压位阶的关系造成信号错误。8B/10B编码采用冗余方式,将8位的数据和一些特殊字符按照特定的规则编码成10位的数据,根据这些规则,能检测出传输过程中发生错误的信息。通过以上各种措施,8B/10B编码方式能够确保数据在高速传输过程中正确传送和识别。

因此这里提出一种利用FPGA实现8B/lOB编解码系统设计方案。

1 系统设计总体设计

1.1 系统设计结构

该系统是基于FPGA设计的8B/10B编解码器,首先系统接收外部发送的8B并行数据,在8B/10B编码模块中完成编码后,再通过10B数据并串转换模块生成利于传输的10B串行信号。这样8B/10B编码模块和10B并串转换模块构成8B/lOB编码器。编码端发送的10B串行信号经过传输线路传输后被lOB数据串并行转换模块所接收,转换完成的10B并行数据再通过1OB/8B解码模块解码完成后即是还原后的原始数据。这样lOB串行数据到10B并行数据转换模块和1OB/8B解码模块就构成了1OB/8B解码器。图1为系统设计框图。

1.2 设计方案

8B/10B编解码器通常有两种设计方法:一种是用查找表直接将8位信号映射成lO位信号,该方法是采用存储器存储所有可能出现的码组,再将输入码组转换为存储地址,找出对应的编解码。这种方法逻辑简单,开发时间很短;另一种是通过逻辑运算直接实现编解码功能,其优点是明显减小内部使用面积,但逻辑关系复杂。从系统优化考虑把1节8 bit字节拆分成3 bit和5 bit,然后在极性偏差RD(running dis-

parity)控制器的控制下以并列方式编解码。这种方法的组合逻辑实现可以简化码表,减小电路板的面积,有效提高编码工作速度,同时由于电路板的面积减小,功耗显著降低。这里采用第1种方法,同时结合第2种方法的设计思路。

2 系统软件程序设计

2.1 8B/10B编码模块

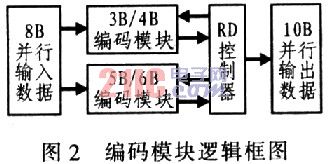

8B/10B编码模块是整个系统主体部分之一,该模块在逻辑上又分成3B/4B编码模块、5B/6B编码模块、RD控制模块等3部分,如图2所示。编码器首先将接收到的8B数据分成3 bit和5 bil两部分,然后分别编码成4 bit和6 bit,编码完成的4 bit和6bit再按顺序组合成lOB码。整个系统首先将3 bit编码成4 bit,RD控制器读出4bit数据的RD值,然后反馈控制5B/6B编码模块选择合适的编码。最终RD控制器判断10B数据的RD值,若满足要求则输出,否则将报错。系统采用的编码列表主要包括以下4种编码:

1)“1”和“0”相邻的完美平衡代码例如,通过查找3B到4B(简称3B/4B表)与5B到6B编码表(简称5B/6B表)可知,如编码“1001”与编码“010101”,该类编码的RD值为0而且与其他任何形式的代码组合都不会出现RD值超过±2或者连续的“0”“1”超过3个的情况,所以该类代码采用一对一的关系。

2)“l”和“O”有间隔的完美平衡代码例如,3B/4B表的编码-3“1100”和“0011”与5B/6B表编码-7“111000”和“000111”,该类编码的RD值为O,与其他代码组合不会出现RD值超过±2的情况,但是会出现过多的连续“0”“l”的情况。所以该类代码采用一对二的关系。例如5B/6B表的编码-7,如果采用“111000”和4B码末位为“1”的代码组合就会出现连续的“1”超过3的情况,此时就应该采用“000-111”来避免该情况的发生。

3)“l”和“0”有间隔的不平衡代码例如3B/4B表的编码4-“0100”和“1011”、“0010”和“110l”,5B到6B编码表的编码4-“110-101”和“001010”,该类编码的RD值是+2或者-2,与其他代码组合有可能出现RD值为±4的情况,所以该类代码也采用一对二的关系。例如5B/6B表的编码4,如果与RD值为+2的4B代码组合时就采用RD值为-2的“001010”代码,反之与RD值为-2的4B代码组合时就采用RD值为+2的“110101”代码。如果与RD值为0的代码组合时就随意采用一个代码即可。

4)3个连续“1”或“O”的不平衡代码例如3B/4B表的编码7-“0001”“lll0”“1000”“0111”,该类代码与其他代码组合时的RD值问题同于第三类代码的处理方法,为了防止更多连续“l”或“0”出现,提供了4种代码选择,结合具体情况特殊考虑。

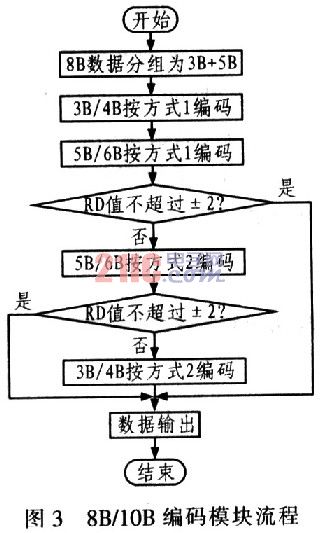

通过上述对编码代码列表的讨论,不难看出在实际的程序设计中需要避免如下3种情况出现:RD值为+2的4B代码和RD值为+2的6B代码组合;RD值为-2的4B代码和RD值为-2的6B代码组合;连续4个或4个以上的“0”“l”的代码。前两种情况可通过代码分组4B和6B代码,轮流选择6B和4B代码的方法,该方法可以通过状态机实现。程序流程如图3所示。

2.2 10B并串转换模块

该模块主要完成10B并行数据到lOB串行数据的转换功能,lOB串行数据的数据格式为:lbit低电平起始位、10 bit数据位、l bit高电平停止位、2bit高电平数据空码。生成一个完整的10B串行数据包含4个状态,生成起始位、转换10 bit数据位、生成停止位、生成数据空码。

2.3 10B串并行转换模块

该模块主要完成10B串行信号到10B并行信号的转换,10B信号的串并转换模块主要是要从14 bit的串行信号中挑出10bit的有效数据位,过程中首先要判断起始位(而不是任意一个低电平),然后采集10bit的有效数据位,完成后等待下一个起始位。程序同样是通过状态机来实现整个过程的流通。

2.4 10B/8B解码模块

解码模块根据系统要求可分为6B/5B解码模块、4B/3B解码模块和误码检测模块。解码模块相对编码模块而言逻辑过程要简单的多,该模块首先将10bit信号分割成4 bit和6bit两部分(高低位必须和编码端对应),然后4 bit和6 bit数据根据编码列表分别解码成3 bit和5bit,在解码过程中判断是否有误码产生有则报错,无则并行输出。图4给出了1OB/8B解码模块的逻辑框图和程序设计流程如图4所示。

3 系统仿真结果分析

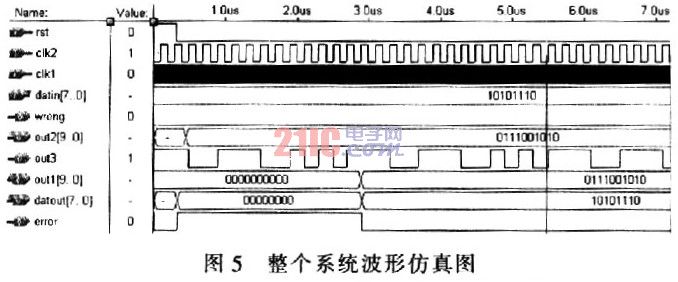

待完成整套的8B/10B编解码器模块连接后,对整体程序进行仿真验证,其结果如图5所示,其中clkl为编码和解码模块的时钟引脚,elk2为1OB串并转换和10B并串转换模块的时钟引脚,rst为整个系统的异步复位引脚,datin[7..0]为待传输的8bit并行数据,datout[7..0]为传输完成的8bit并行数据,error为解码端误码检测报警引脚,wrong为编码端出错报警引脚。还有3个引脚是系统不必要的但是为方便调试而引出的,outl[9..0]为10B串并转换完成的10B并行信号,out3为10B并串转换完成的10B串行信号,out2[9..0]为8B/10B编码完成的10B并行信号。

由图5可看出:输入数据datin为“10101110”,经过8B/10B编码完成的数据out2为“0111001010”,8B/10B编码模块出错报警引脚为“0”,10B并串转换输出的串行数据out3为“00111001010111”,10B串并转换输出的并行数据outl为“0111001010”,1OB/8B解码完成的输出数据datout为“10101llO”,结合整个系统的工作过程和编码列表不难看出系统正确的完成了编码和解码的功能,能满足设计任务的需要。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网