作者:Steve Leibson, 赛灵思战略营销与业务规划总监

Jan Gray是在FPGA中集成32位RISC处理器的专家,他写了一篇博客叫作FPGA CPU 新闻,副标题为 “使用FPGA开发并行计算机体系架构”。 Jan Gray的最新帖子为FPGAs, 当时和现在,这篇帖子将1995年 在Xilinx XC4010PC84-5 FPGA中集成J32 32-bit RISC CPU与目前Xilinx Virtex-7 XC7VX690T FPGA 集成同一处理器进行了对比。Gray 使用的J32处理器采用经典RISC架构,带有3-operand操作指令,4=stage流水线(提取、寄存器读、执行、回写),和32位操作数寄存器文件。

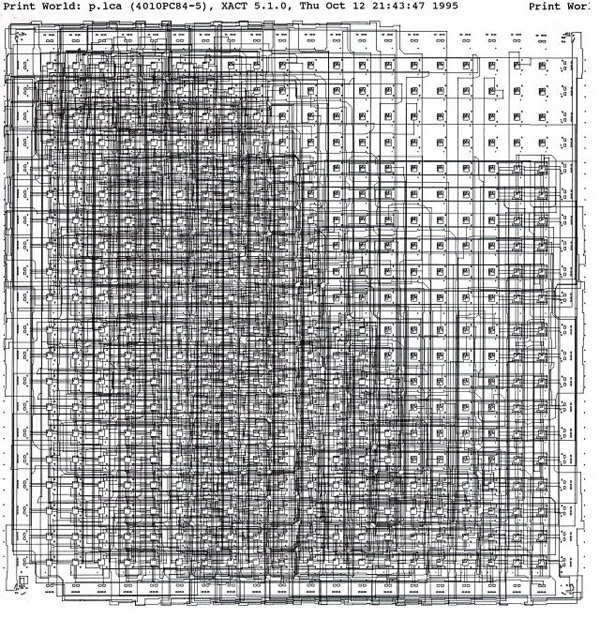

1995年,Gray使用的J32处理器基本消耗了XC4010 FPGA中800个4-input LUT。处理器排列看起来是这样:

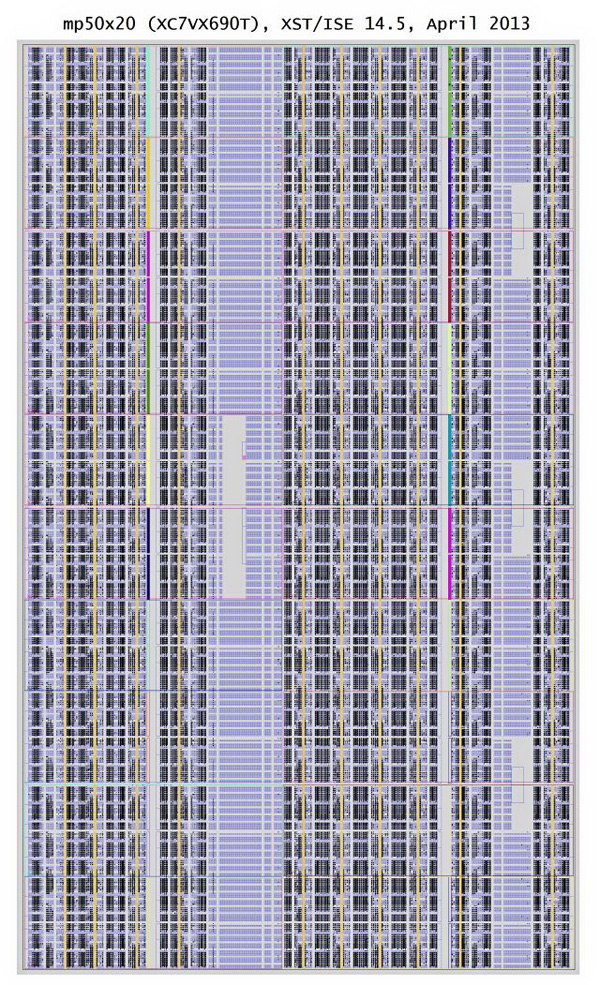

13年以后。同一J32处理器内核集成在Virtex - 7 FPGA,它支持433,000以上的6输入 LUT,是250个路由器核心与1000个处理器互连预留空间的1000倍。J32 RISC处理器的排列看起来像这样:

“也就是说过去18年摩尔定律将每个FPGA集成1K LUT升级至每个FPGA集成1K 32-bit CPU。(顺便说下,规模最大的Virtex Ultrascale 3D FPGA有440万个逻辑单元,所以逻辑容量足够10,000个以上Jan Gray所提到的 32位RISC J32 CPU进行互连。且看以下的注释说明!)

如果在您的系统设计中涉及处理器和FPGA的交互,请点击FPGA CPU News查阅Jan Gray的博客文章。

注:Jan Gray指出,Virtex UltraScale VU440 FPGA拥有2,520 BRAM,因此在Gray设计当中实现直接端口存在限制,它只可用于2520 32-bit RISC处理器内核。也许Virtex UltraScale XCVU160加上更多BRAMS和较少逻辑资源是更好的选择。我将在以后文章中详细说明。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Jan-Gray-s-New-LUT-Math-How...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网