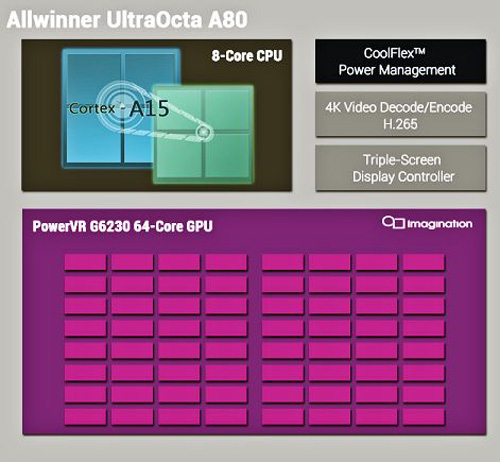

巴塞罗那全球移动大会上全志(Allwinner Tech)推出用于移动电话、平板电脑和其他便携式产品的UltraOcta A80移动应用处理器。该UltraOcta A80处理器除集成基于Imagination Technologies的64-core PowerVR 6230 low-power GPU 处理器外,还集成基于ARM’s big.LITTLE processing technology 的4个ARM Cortex-A15处理器和4个ARM Cortex-A7处理器。以下为AllwinnerUltraOcta A80移动应用处理器(出自Imagination Technologies网址)的AllwinnerUltraOcta A80移动应用处理器图片:

全志UltraOcta A80移动应用处理器框图

如果没有最初的原型和验证,将无法制造巨型八核系统芯片。全志使用基于FPGA的原型系统Synopsys HAPS-70 进行原型设计和验证。全志科技CTO丁然称:“HAPS系统性能超出我们的需求,我们的设计师能够对本公司最大的芯片系统进行准确校验。”

Synopsys公司基于FPGA原型解决方案产品营销总监Michael Posner发布一篇博客,对全志开发UltraOcta A80移动应用处理器过程当中使用Synopsys HAPS-70系统进行了记录。他写道:

“运行CPU和GPU,最终将涉及运行大量的硬件/软件,这些硬件/软件相互影响,我们知道这些运行硬件/软件需要进行大量的效验,以确保这些硬件和软件不存在程序错误。HAPS基于FPGA原型具备高性能,可运行大量的测试,减少发现程序错误的概率。”

在Posner的博客中,他随后提出了芯片系统原型设计及校验如AllwinnerUltraOcta A80应用处理器的大型芯片系统时所出现的关键困难点:

“基于FPGA的原型建模GPU的一个问题是事实上GPU通常远远大于单个FPGA(嘿,这有悖基于FPGA原型的三大规律之一)。因此我们使用HAPS多FPGA系统帮助解决问题。首先我们利用HAPS软件工具分割多个FPGA间的GPU设计。以下的框图是一个典型的GPU分区抽象图。请注意,多个FPGA当中的1000个信号。FPGA没有提供这么多的引脚,因此需要使用HAPS高速时域多路复用技术打包这些信号,并在各个FPGA之间使用高速连接技术发送,发送速度为1Gb/ s。”

HAPS-70基于FPGA原型系统多个FPGA之间的分区

HAPS-70系统基于Xilinx Virtex-7 2000T 3D FPGA,提供巨大的逻辑容量(2M逻辑单元),以及高速串连(36个12.5Gbps收发器),以支持HAPS70基于FPGA原型系统的多个FPGA芯片系统原型功能。

以下为Synopsys视频,你可借此深入了解HAPS-70基于FPGA原型系统:

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Allwinner-uses-Synopsys-HAP...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网