作者:Steve Leibson, 赛灵思战略营销与业务规划总监

与DDR3 SDRAM相比, Hybrid Memory Cube混合存储立方体(HMC)是一种3D IC存储器件,可提供15倍的性能,功耗同时降低70%。通过多个高速串行链路与主机CPU或FPGA连接。HMC设计在存储器管芯堆栈的底部放置一个逻辑芯片。HMC 3D堆栈中的逻辑芯片管理所连接的DRAM,并通过纵横制结构来呈现系统的剩余部分,该部分通过多个高速串行链路将系统与模组的DRAM片相连。

HMC项目证明了存储器是一个杀手级的3D应用。HMC通过DRAM管芯堆栈运行很多TSV (硅通孔) 访问各个管芯DRAM阵列的固有并行。在HMC堆栈中的每个固有的DRAM管芯具有多个独立的存储阵列,导致大量潜在并行,因此需要大量的潜在内存吞吐量。通过TSV实现大量DRAM互联使得海量带宽成为可能,多个片上DRAM堆栈上的潜在带宽已经在存储器管芯上存在数十年,现在终于可以得到充分利用,用来实现更多的系统性能。

利用多核处理设计状况下,这种额外带宽的不断增加显得非常重要。多核处理器芯片对内存带宽的胃口永不满足,HMC表明,3D IC封装是实现所需的内存带宽的一种方式。如果这一切看起来像非常新的存储结构,那么它需要新的存储控制器—您的想法很正确。

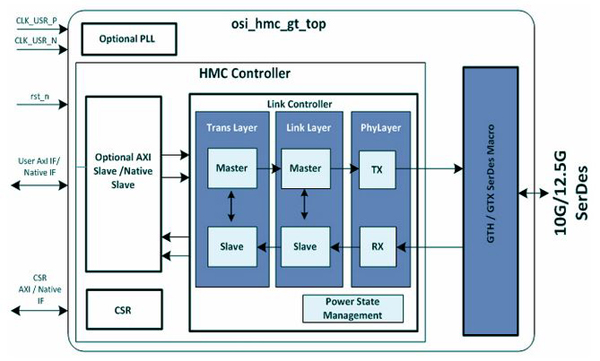

Open-Silicon刚刚发布 HMC控制器IP,它利用10Gbps或12.5Gbps链路连接与管理HMC rev2 设备。该控制器IP支持半带宽(8通道)和全带宽( 16通道) HMC操作,并设有4.0 AXI系统接口。并对Xilinx 7系列可编程逻辑器件进行了优化。以下为 Open-Silicon HMC控制器的框图:

Open-Silicon HMC控制器IP在Xilinx Virtex-7和Kintex-7 FPGA利用多个GTX ( 12.5Gbps)和GTH ( 13.1Gbps )收发器。

Open-Silicon对新型HMC控制器IP提供评估平台 。该平台基于Xilinx的Virtex- 7 XC7VX690T FPGA,包括集成HMC控制器以及HMC实验程序功能并且是完全经过验证的参考设计。HMC实验程序功能以及软件协议栈可快速评估Open Silicon HMC技术和HMC技术的性能。

注意:有关使用高速SerDes收发器的串行连接存储器的更多信息,请参阅“DDR4是否是最后的SDRAM协议?” SemiWiki的Eric Esteve说—是的。那么替代产品是什么呢?”

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Controller-IP-mates-FPGA-to...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网