作者:Steve Leibson, 赛灵思战略营销与业务规划总监

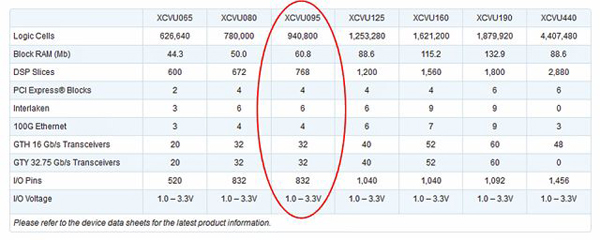

Xilinx今天宣布,首批20nm Virtex UltraScale FPGA—XCVU095器件已经发货。这批器件是在1月份投片的。(参见“20nm新闻:Virtex UltraScale投片…关于UltraScale,你可能不知道的12件事。”)

这批20nm Virtex UltraScale FPGA的发货时间比20nm Kintex UltraScale器件的首次发货时间晚了6个月,你也许会问“高端20nm Virtex UltraScale FPGA和中端20nm Kintex UltraScale FPGA的区别是什么呢?”

这两个系列的器件都是基于UltraScale架构,包括许多布线能力方面的改善,都整合到了协同开发Vivado设计套件的最新版本中。当然,20nm Virtex UltraScale和Kintex UltraScale

器件在容量方面有差异,但这两个系列的20nm UltraScale器件都是基于许多同样的基础架构,包括逻辑单元、Block ram以及DSP Slice(关于UltraScale架构中新的、改进过的DSP48E2,可以参见“UltraScale DSP48E2:每个Slice上有更多的DSP”)。

这两个系列的器件也都内置16Gbps GTH SerDes收发器。

去年首批Kintex UltraScale器件出货时,这些共享的构件模块都已经通过了硅片验证,而通过这次Virtex UltraScale器件的发货,又有3个主要的20nm构件模块得到验证:

1. 32.75Gbps GTY SerDes收发器(在下一篇博文中会有更多关于它的内容!)

2. 100G 以太网MAC固化IP核

3. 150Gbps Interlaken固化IP核

20nm GTY SerDes收发器能驱动芯片间32.75Gbps的双向数据传输,可以很方便地用于驱动数据中心网络的100Gbps光口以及其它4-lane,100Gbps CAUI-4网络设备。这些应用也可以很好地利用固化的100G以太网MAC IP核。另外,20nm GTY SerDes收发器能直接和一些最新推出的高速芯片进行接口,比如MoSys的第三代最高速度的Bandwidth Engine。(参见“MoSys第三代Bandwidth Engine(更大、更好、更快)需要16个28Gbps lane来…”)

20nm GTY SerDes收发器还能在一个背板上驱动28.21Gbps双向数据传输,这就和固化的150Gbps Interlaken IP核非常相配。在网络设备中,Interlaken的应用已经越来越普及,主要用于高速背板互连。(例如,参见“华为和Xilinx在2014年国际光纤通信会议上揭开400GE核心路由器原型的面纱。FPGA器件挑起了大梁。”)

这三个新的20nm Virtex UltraScale模块,现在已经通过了硅片验证,可以用单芯片来实现400G和500G的系统。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Xilinx-ships-first-20nm-Vir...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网