作者:Steve Leibson, 赛灵思战略营销与业务规划总监

ADI公司新的AD9144BCPZ器件集成了4个16bit DAC,可以工作在2.8GSPS采样率,允许高达奈奎斯特频率(Nyquist)的多载波生成。主系统的数据通过一个8-lane的JESD204B串行接口进入到四通道模数转换器,该接口有助于降低器件的功耗:1.5W。AD9144BCPZ售价80美元(1000片的订量报价)。AD9144的支持资源包括一块价值495美元的AD9144-EBZ评估板以及一个FPGA夹层板(FMC)I/O连接器,用于和主板,比如Xilinx评估板进行装配,还包括软件、开发工具、SPI控制器以及参考设计。

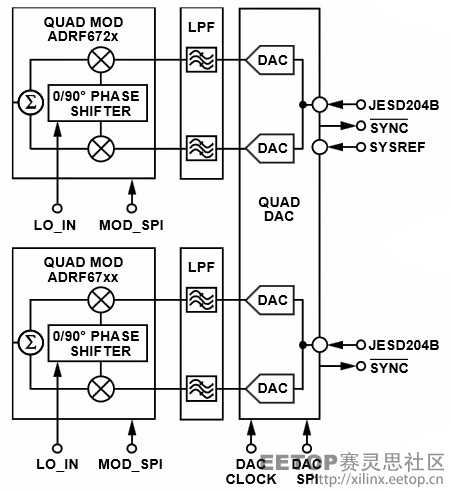

AD9144 DAC的输出经过优化,可以和该公司的ADRF672x模拟正交调制器(AQMs)进行无缝连接。如下图所示:

要深入了解更多关于用于高速数模转换器(DAC)和模数转换器(ADC)的JESD204B接口的信息, 可以参见“JESD204B Reference Design and FPGA Debug Software from Analog Devices Accelerates High-Speed ADC-based Systems Design,” 和 “Want a quick tutorial on serial interfaces (LVDS, JESD204B) for analog data converters?”两篇文章。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Quad-16-bit-DAC-with-8-lane...

© Copyright 2014 Xilinx Inc.

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网