作者:Steve Leibson, 赛灵思战略营销与业务规划总监

这篇连载博文一直在探讨如何驱动Adafruit NeoPixel RGB LED条。在前面的两篇博文中,我已经介绍了NeoPixel的驱动波形、NeoPixel连接的硬件以及NeoPixel的电源要求,现在是时候来分析一下这个设计方案的架构了,该架构是采用Zynq SoC中的PS(处理器系统)和PL(可编程逻辑)来实现的。

先回想一下需求,我们想要驱动可变数量的NeoPixel,这些NeoPixel要能够单独编址,并且在程序执行的时候,每一个像素要能够独立地进行升级。

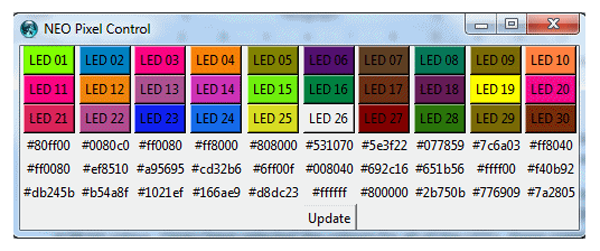

让我们把需求再扩大一些,在我的脑海中第一次考虑这个示例方案时,我在笔记本电脑上编写了这样一个图形界面,我要驱动的阵列中的每一个LED都有一个按钮与之对应。当我点击一个特定的LED按钮时,我想要能给这个LED选择一个24位的颜色。一旦我为所有的LED都选择了颜色,这些命令将会被下载到Zynq中,用于更新NeoPixel的状态。

NeoPixel图形界面

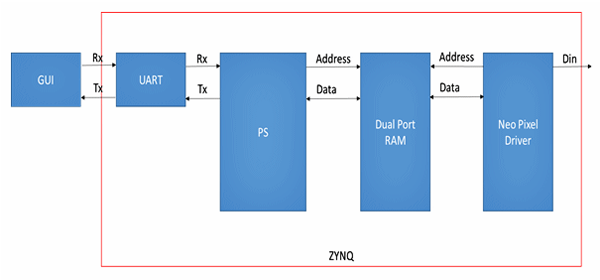

很显然,PS将用于处理跟图形界面程序之间的所有通信,保存像素的值,并把这些数据都传输给PL中自定义的NeoPixel驱动器。为了保证通信的可靠性,我需要定义一个简单的数据传输协议。

这就意味着我们需要在器件的PS和PL之间传输数据,这是这个范例的全部设想中的一部分工作。我想到要使用一个双端口RAM来实现PS和PL之间的通信,它可以让PS把像素值从一个端口中写入,而PL则从另外一个端口中把数据读出。

在这块RAM中,每一个像素都被分配了一个地址,每个存储单元都保存了8位的绿色、红色和蓝色值。BRAM的首地址用于存储所要配置的像素的数量,如果把首地址的值设置为0,则NeoPixel阵列就不能被更新了,这就相当于是一个使能信号。

因此,可以把这种处理方式表达为下面这个系统方案框图:

系统框图

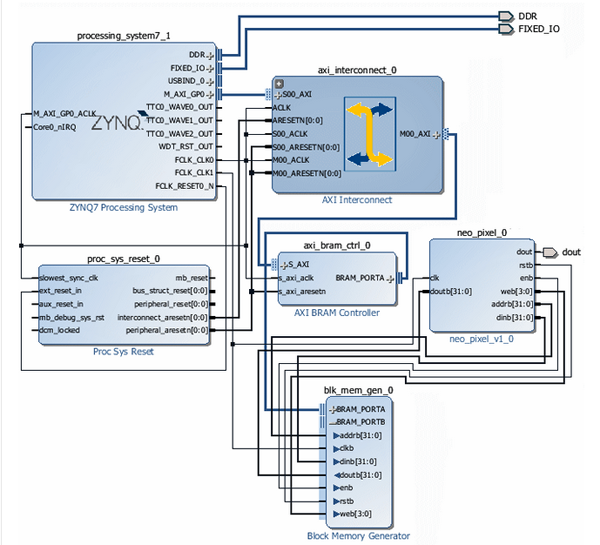

非常有帮助的是,在Vivado IP集成器中,已经有了很多IP库所提供的IP模块,可以用来实现我想要的功能。这些IP模块有两个好处,一个是可以节省我用来实现这个方案的时间,另一个是可以让我把设计精力都聚焦在那些最能体现我价值的地方。(对于商业应用来说,这非常重要)

除了PS和PS复位模块之外,设计方案还会使用以下IP模块。

• AXI互连矩阵 – 用于在PL内部实现灵活的AXI总线连接。在这个方案中,只需要有一个AXI主模块。

• AXI Bram控制器 – 用于通过AXI互连总线与BRAM模块进行连接,这样,PS可以通过这个控制器模块来访问BRAM存储器。

• 双端口BRAM – 一个端口连接在AXI BRAM控制器上,另一个端口与自定义的NeoPixel驱动器相连。

下面是该完整方案的框图:

到了这个时候,万事俱备,就只差编写NeoPixel驱动器了。我将在下一篇博文中进行说明。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处