作者:Steve Leibson, 赛灵思战略营销与业务规划总监

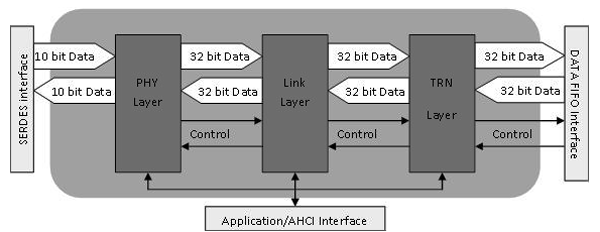

IntelliProp的SATA 6Gb/s Host IP核刚刚在新罕布什尔大学互通测试实验室(UNH-IOL)通过认证测试。目标器件使用的是Xilinx Kintex-7 FPGA器件。据IntelliProp所说,“IntelliProp SATA 6Gb/s Host IP核是UNH-IOL在Xilinx Kintex-7器件上认证通过的第一个SATA Host IP核”。该IP核实现了SATA协议的PHY(物理层)、Link(链路层)和TRN(传输层),支持1.5、3和6Gbps传输速率,和SATA规范完全兼容。

这是一张IntelliProp SATA IP核的框图:

关键特性包括:

• 与SATA1.5Gb/s、3.0Gb/s以及6.0Gb/s业界规范完全兼容

• 传输或者AHCI或者应用或者应用寄存器(ARI)接口可选

• 数据接口采用FIFO设计

• 支持SerDes、PIPE或者SAPIS中的任一接口

• 同步设计,易于集成

• 可综合的Verilog设计

• 支持Verilog/VHDL

• 支持Power模式(局部省电/睡眠)

• 支持内建自测(Built in self test)

您的下一个设计中,就可以使用这个SATA Host IP核。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/SATA-3-0-6Gbps-host-IP-core...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网