作者:Steve Leibson, 赛灵思战略营销与业务规划总监

你可以将两块FPGA甚至是两块FPGA板捆绑在一起,使用并行或串行I/O以及Chip2Chip LogiCORE和AXI IP的组合,使他们相当于一个器件进行工作。这在新的应用笔记“AXI Chip2Chip Reference Design for Real-Time Video Application” (XAPP1160)中有展示。这个文件的重点在于在两块Kintex-7 FPGA KC705 Eval板之间或者在一块Kintex-7 FPGA KC705 Eval板和一块Zynq-7000 AP SoC ZC706 Eval板之间传输实时高清视频流,两板之间通过FMC HPC接口连接。

这里的基本概念是FPGA或者SoC中的具体化的IP和FMC-to-FMC线连接“消失”了,一块All Programmable器件上的其他逻辑认为它是在与传统的AXI端口对话,同时发送出去的和接收到的数据传播了一段距离,就像是它开创了一条连接线缆的道路并且在另一块板的All Programmable器件中的AXI端口上出现。把它看作是AXI的瞬间移动。

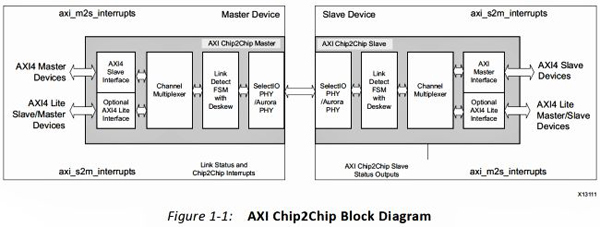

这里有一张来自“LogiCORE Chip2Chip产品指南” (PG067)的简单框图,用来说明基本概念

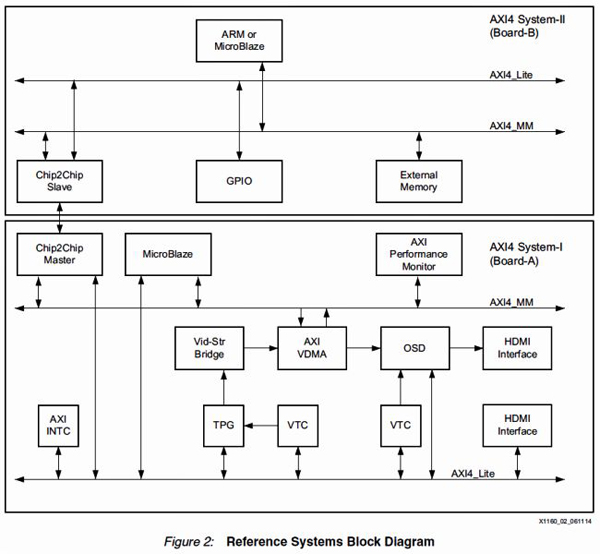

这里是来自“AXI Chip2Chip Reference Design for Real-Time Video Application” (XAPP1160)应用笔记的更详细的参考设计方块图。

这里是来自“AXI Chip2Chip Reference Design for Real-Time Video Application” (XAPP1160)应用笔记的更详细的参考设计方块图。

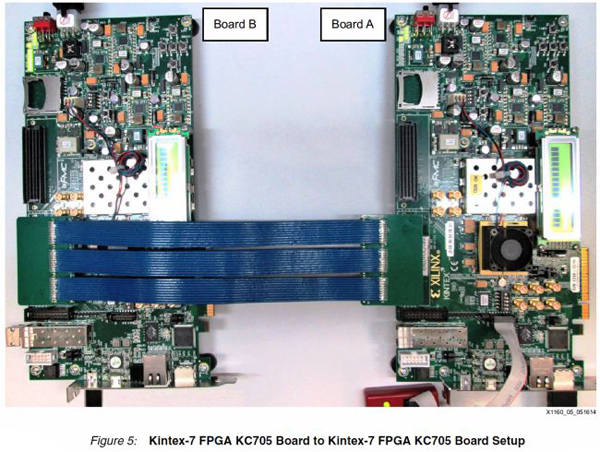

操作说明书中的一张图片,展示了使用跨板FMC接口的内部链接方案将两块Kintex-7 FPGA KC705板捆绑在一起。

在连接Kintex-7 FPGA和Kintex-7 FPGA的设计中,设置64位 AXI Chip2Chip主实例为物理层以频率为200MHz运行的独立时钟模式。在连接Kintex-7 FPGA和Zynq-7000 AP SoC设计中,使用32位的AXI数据宽度来减少在设计中的I/O信号数量。KC705-to-KC705系统在板子间发送1920x1080p60的视频。拥有较窄AXI位宽的KC705-to-ZC706系统在板间发送720x480p60的视频。

关于参考设计的更多的详细信息,见应用笔记。

© Copyright 2014 Xilinx Inc

如需转载,请注明出处