作者:Steve Leibson, 赛灵思战略营销与业务规划总监

Rok Uršič是Instrumentation Technologies公司的创始人以及CEO,是一位在尖端粒子加速器诊断测试仪器领域的世界级领军人物,他在1998年创立了这家公司,其测试仪器技术团队已经研制了针对粒子加速器的复杂测试仪器。从某些方面看,这其实是一个很好的市场,并且公司已经在这个领域相当成功但这是一个利基(Niche)市场,所以Rok Uršič期望公司能进一步扩张并将其设计团队带入一个更加广阔的全新领域。当Zynq SoC出现后,他们觉得机会来了,利用Zynq SoC芯片,他们打造一个新平台,这个平台具备当前粒子加速器的复杂测试仪器的大部分特性,同时还可以在更广阔市场上获得应用。

这正是Red Pitaya真正目的所在。

对于设计团队来说,下一步需要做的是如何开发与创建这个平台。首先,要创建3D模型,以便人们可以获得这个产品大小的概念。然后,他们以标语“Red Pitaya:全民所有的开源测试仪器”进行Kickstarter竞标。Kickstarter募集资金目标为$50,000,而最终募集到$256, 125,超募达到5倍多,并由此开始进入实施开发进程。

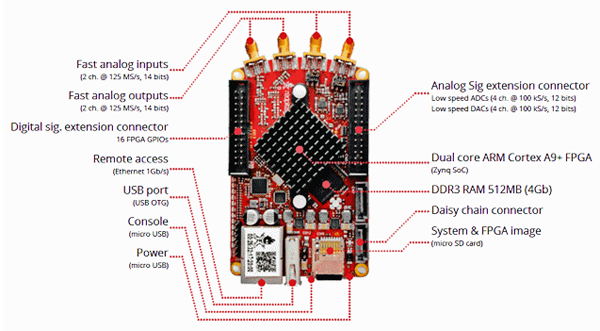

Red Pitaya的硬件核心主要是一块单板,这块单板具备快速模拟输入输出、数字输入输出、强大的处理资源以及很好的I/O性能。板上有两组14比特125Msamples/sec模拟输入,两组两组14比特125Msamples/sec模拟输出;四组低速12比特100ksamples/sec模拟输入,以及四组低速12比特100ksamples/sec模拟输出;I/O方面,拥有1Gbps以太网接口,一个USB OTG接口和一个USB控制端口。计算能力方面主要得益于ARM Cortex-A9多核处理器以及一大组不受约束的FPGA架构DSP,这些资源均来自于板上的Zynq SoC芯片。板子的图片如下。

起先,设计团队并不确定他们是否需要用到SOC芯片,但他们很清楚他们得需要一片FPGA来实现某些功能,同时,他们还需要一个微处理器。所以他们也在考虑其它方面的解决方案,Zynq SoC所具备的特性让设计团队意识到选择一个All Programmable SOC芯片将是一个正确的选择,因为当他们使用分立的微处理器与FPGA来实现时,无法满足处理器与可编程硬件之间的带宽要求。Red Pitaya在尚未命名之时,设计团队其实心中已经有了一个清晰设计蓝图:快速数据采集、快速数据生成以及输入输出之间的快速反馈环路,使用SOC芯片的方法可以获得巨大的好处,使用Zynq SoC芯片可以为Red Pitaya的开源应用创建更多的机遇。

Red Pitaya开发团队在使用赛灵思可编程器件方面有非常长的历史,从Virtex-II FPGAs一直使用到Virtex-6,相对于微处理器,基于ARM处理器方面是受到经验限制,因此后来转移到英特尔x86处理器,不过x86并不是很适合Red-Pitaya,主要是功耗方面问题,在找到Zynq之前,他们并没有更合适的选择,而Zynq内嵌处理器是最吸引Red Pitaya设计团队的。

事实上,在FPGA成为设计团队一个主要考虑之前,Zynq SoC芯片就已经出现了,很多人不太熟悉FPGA是源于他们对使用FPGA存在顾虑。而Zynq SoC独具匠心地把处理器与FPGA结合与应用,可以在使用FPGA的同时,轻松的使用处理器。假如你是一位软件工程师,你可以从熟悉的ARM处理器入手写代码,之后就可以考虑使用FPGA来加速你的进展,这是减少障碍的一个简单方法。若你以沉迷于FPGA方式开始,最终你会体会到其优异性能的巨大好处。

对于想打造一款完全开源产品的Red Pitaya设计团队来说,这种特性正是他们梦寐以求的 ,使用内嵌处理器的FPGA这种方法也正是他们需要的,使用FPGA内嵌处理器软核进行系统设计的门槛是比较高的。同样一个设计团队,如果考虑使用多年以前带PowerPC处理器的赛灵思Virtex-II Pro器件来做设计,是无法充分利用FPGA与处理器的全部性能的,而使用Zynq SoC,则可以充分发挥该芯片内所有性能特性。

基于希望全球更多的社区团体能为产品开发测试应用的开源思路强烈地激励着Red Pitaya设计团队,而Zynq SoC因为首先从CPU开始启动,人们就很容易利用熟悉的处理器编程模式来创建一个新的应用,而之后,他们可以考虑以全新的方式来利用片上FPGA逻辑。

在使用 Zynq SoC之前,Red Pitaya的早期设计里面包括一些快速RF输入输出和一些比较低速的模拟输入输出(大概每秒几千次采样),仅仅是打算用来连接微处理器。而Zynq SoC集成了ADC,可以直接用于低速模拟输入(注意,这里“低速”指100ksamples/sec左右),可以使用DAC作为Zynq SoC的快速与低速模拟输出。

相较其它类似的方案,Zynq SoC功耗很低,举个例子,使用x86处理器的方案功耗都会比较大,需要一个散热风扇,而Red Pitaya仅仅需要一个无源散热片。

对于Red Pitaya设计团队来说,Zynq SoC众多特性与好处中最重要的是:

1. 处理器系统与可编程逻辑之间的带宽是首要的;

2. 功耗其次;

3. 由CPU先行启动的启动顺序也是非常重要的。

设计团队知道他们选择的FPGA速度性能足以让他们可以选择价格低廉的ADC和DAC,比如说,他们也知道他们并不需要使用500MHz的高性能ADCs,但是,CPU、FPGA和内存之间的带宽性能是至关重要的。就这一点而言,Zynq SoC的架构是非常有利于Red Pitaya设计团队的。

几年前,设计团队在设计粒子加速器测试仪器时,在Virtex-II FPGA的RocketIO MGT SerDes端口配置上积累了丰富的经验,当时,他们并不知道在高速私有网络上使用哪类串行协议?因此,具备灵活性的Rocket I/O是最合适的。一个团队设计成员曾说:“我们获得了很好的支持,我们不能因为几个美分或因一点点价格差别而扔掉所选的器件,而且,当你习惯于某一类具体的器件时,你并不想任意切换到别的器件”。

设计团队曾经尝试至少一家其它供应商的FPGA器件,但供应商的支持并不好,也有一些技术上的问题,举个例子,在使用某厂商的FPGA器件时,设计人员不得不使用许多FPGA固定资源来实例化一些东西,而在赛灵思的器件中,这些已经以硬核的形式进行固化了。另外,使用竞争对手的FPGA的资源消耗远远超出预期。

这就是为什么测试仪器技术的设计团队一直使用赛灵思器件的主要原因。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/The-Genesis-of-the-Zynq-bas...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处