者:Frank Melinn 赛灵思公司杰出工程师 FrankM@Xilinx.com

赛灵思UltraScale器件的28 Gbps 背板功能让网络能够以1 Tbps 的速率运行。

两年前,IEEE 的一篇报道指出,根据当时发展趋势,通信网络在2015 年需要支持1Tbps 的容量要求,到2020 年则需要支持10 Tbps 的传输能力。根据2012 年的这份报告,明年将有近150 亿台固网和移动网络设备,其中包括机器间的互联。对于光传输网络(OTN)应用,核心节点的每波长带宽到2015 年预计将达到100G 到400G,2020 年将提升到近400G 到1T。

赛灵思Virtex® UltraScale ™ All Programmable FPGA 是高端FPGA 系列的扩展,可支持1Tbps 系统的实现。Virtex UltraScale 系列具有前所未有的高性能、系统集成度和带宽,适用于有线通信、测试测量、航空航天与军用以及数据中心等各种不同应用。

很多公司都表示了对1Tb 网络应用的需求。这些应用要求收发器能够直接驱动25G/28G 背板,以解决可布线性、串扰、差分插入损耗和阻抗匹配等问题。而Virtex UltraScale 器件则完美解决了这些难题,无需重定时器即可支持25G/28G 背板操作,从而实现了对1Tbps 应用的支持。

使用外部重定时器会产生可靠性问题,同时还需要占用大量非常昂贵的PCB板级空间。

实例1-Tbps设计

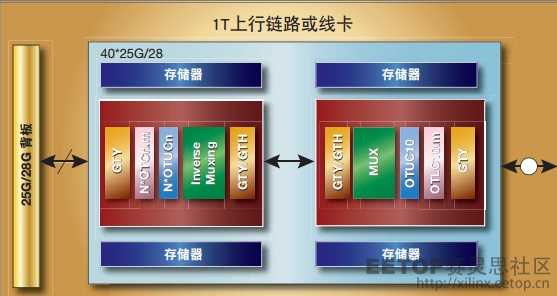

图1 是可能的通用1Tbps 系统的高层次方框图。从图中可以看到,多个带宽低于1Tb 的支路板(此图中有两个)通过在运行速率为25G/28G 的背板与一个1T 线卡相连。

图2、3 和4 是三种可能的1Tbps以太网和OTN 应用的更详细的方框图, 它们全部以Virtex UltraScaleFPGA 为基础进行构建。33 GbpsGTY 收发器可能与CFP2/4 LR4 光学模块以及 25G/28G 背板连接。根据图示,16 Gbps GTH 收发器与高速存储器相连。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网