By Roger Fawcett, OmniTek

电影与电视工程师协会(SMPTE)的6-Gbps和12-Gbps的SDI标准(支持4K60视频)才刚刚被发布,而支持同样分辩率的 HDMI2.0和DisplayPort也才处于应用的早期阶段。鉴于4K UHD电视的强烈消费需求,许多专案标准已经蜂拥而来,势图填补这一空白。事实上,4K UHD电视的诸多地方还在不断变化,系统需要有足够的灵活性,以适应发展中的标准。为确保灵活性,可以将这些设计中常用的陈旧芯片组和ASSP替换为 All Programmable器件,比如赛灵思FPGA和赛灵思Zynq SoC。这些解决方案除了可以提供所需的灵活性外,同时还带来媲美ASIC的性能表现。赛灵思为4K电视设计师提供了大量的帮助——相比于从头开始设计系 统,使用All Programmable器件的时间成本和金钱成本则要低许多。

新的4K UHD电视意味着4倍于之前抢手的高清标准像素数。也许对用户最重要的是,4K允许他们升级到一个更大的电视,在图像质量没有任何损失的情况下提供一种更 加身临其境的感觉。然而,开发支持4K视频的系统存在许多技术上的固有挑战。其中一个是,以60 Hz帧速率传输3840×2160的帧意味着像素填充率高达600Mhz,实时处理该速率需要一个非常高性能的系统。

再就是4K拥有多种不同的传输配置(所有配置都涉及多个数据流,其中一些在同根电缆上通过多数据流复用进行传输,而另一些则使用不同电缆进行传 输),同时还存在不同的新兴技术来支持不同传输配置:4x3G; 6G-SDI和12G-SDI;HDMI1.4和2.0;DisplayPort1.2;以及V-by-OneHS。

另一个设计者面临的问题是该系统不仅需要处理4K,也要处理许多甚至是全部目前正在使用的视频标准,包括标清。此外,系统必须支持不同标准间的转 换,这些相关问题包括向上转换/向下转换/交叉转换,色域不匹配,色彩校正,隔行和非隔行扫描,以及时序处理。其它可能需要的处理还包括降噪,裁剪和大小 调整,所有这些都需要实时完成。有些系统可能还需要处理高速带宽数字内容备份保护(HDCP)。

设计任何系统的第一步是找到设计中可以使用的现成模块。在FPGA领域,PCB设计中可供各式芯片集成的构建块是IP核。4K系统设计两个特别有用的核心是:Omni-Tek的OSVP V2可扩展视频处理器和多通道流式DMA控制器,两者都适用于赛灵思7系列FPGA和Zynq SOC。

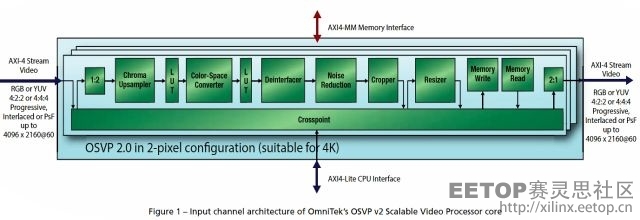

该OSVP V2的特性包括六轴色彩校正; 运动和边缘自适应去隔行(完整带有3:2和2:2电影节奏检测和处理);重调整大小以及锐化和平滑图像;还有降噪。单个OSVP V2内核可以处理多个视频通道。图1给出了该核心的框图。

然而通过PCI Express采集和播放单通道或多通道4K60视频,需要一个DMA控制器,用于优化处理PCIe接口传输的流式数据。OmniTek的多通道流式 DMA控制器有几个关键的特性在这时会很有用。第一个是基于FIFO的DMA(FDMA),可以在需要时旁路数据进出存储器。第二个是一系列的设计优化, 使得控制器可以高效利用PCIe带宽,这些优化包括分散聚合模式描述符的预取以及背靠背TLP数据包的打包。

OmniTek4K UHD视频开发相关的另外一个IP核可以将双采样交错格式组成的4K视频分解成不同数据流。另外,对基本MIG SDRAM控制器进行了替换,从而进一步提高了UHD电视视频应用的性能。

赛灵思对基于FPGA和SoC的4K视频系统设计人员做了进一步支持。首先,Zynq SoC的存在,为高性能视频或图像处理提供了强大的软硬件组合处理能力。Zynq SoC中丰富的DSP可编程逻辑资源为DSP设计者提供了一个高度灵活的平台,他们可以在该平台上实现复杂的信号处理算法,同时,处理器和可编程逻辑之间 的紧耦合使得在两个结构域中都可以开发编解码器算法。基于Zynq SoC的设计也可以降低功耗和成本,因为您仅需要一个高度集成化的设备,否则实现同样的功能您可能需要多个ASSP。

第二,赛灵思的Kintex-7 FPGA和Zynq SoC可编程逻辑可以提供300-MHz的持续视频处理速度,结合1600Mbps的64位DDR3高性能存储器,这对4k视频处理和4K帧缓冲非常关 键。为支持4K视频系统开发,赛灵思器件还提供了丰富的连接件功能,两者都自带了一系列收发器。比如,Zynq 7045 SoC,可提供高达12.5Gbps的收发器,从而允许其连接到12G-SDI,6-Gbps的HDMI2.0,5.4-Gbps的 DisplayPort1.2以及10Gbps的以太网标准。

第三个赛灵思的重要贡献是,IP集成器(IPI)工具以及相关的Vivado设计套件带来了IP集成的易用性。通过IPI,连接IP模块的任务变得 类似于在印刷电路板上连接芯片。符合AMBA AXI4互连协议(赛灵思已经采用为接口标准)的IP块接口处理将相当简单(如连接OmniTek OSVP和DMA块)。

赛灵思新的UltraScale(16纳米/20纳米)技术的出现带来了更强大的功能,它支持的时钟速度可高达数百千兆比特每秒,已经被认为是“ASIC级别”。该UltraScale架构不仅满足4K级别的视频系统开发,更高级别的8K也已经起步。

注:本博客基于Roger Fawcett的一篇较长文章,题目是“Zynq SOC助力4K电视开发”, 它在第89期的Xcell期刊上刊出(稍后您将在本站看到中文版译文)。OmniTek是所有视频系统设计的一个良好IP核来源。特别是其中的两个核心对 4K系统设计很有用:Omni-Tek的OSVP V2可扩展视频处理器和多通道流式DMA控制器,两者都适用于赛灵思7系列FPGA和Zynq SoC。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/4K-TV-Development-Made-Easy...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网