作者:Steve Leibson, 赛灵思战略营销与业务规划总监

Adrian Cosoroaba和Terry Magee在本月MemCon上给出了关于DDR4 SDRAM接口的详细展示,该演示应用于赛灵思UltraScale All Programmable FPGA上。接口设计将DDR SDRAM提升至2400Mbps甚至以上,同时降低接口功耗。为了达到这个目标,赛灵思的工程师们必须将DDR4接口问题放在首位。除了设计将DDR4兼容UltraScale I/O PHY,他们从头设计了DDR4 I/O PHY,然后扩展它的性能并支持其他I/O的需求。结果:基本的13位可编程字节通道,这首先是一个DDR4 PHY。

如果你来自SoC的世界,也许不太明白为什么赛灵思需要选择这样做。因为当有成千上万甚至百万个逻辑单元和触发器、几兆的块RAM和数千个DSP片时,由于物理封装的限制只有数百个I/O管脚,所以,I/O管脚是稀缺资源。所以,I/O管脚必须可编程且足够灵活,可覆盖任何可能的I/O使用范围,从DDR4-2400 SDRAM驱动库到使LED闪烁以及其他更多的事情。这就是赛灵思为何如此做的原因。对于UltraScale架构的FPGA来说,我们首先实现了I/O设计的难点——DDR4 PHY,然后再添加一些简单的。

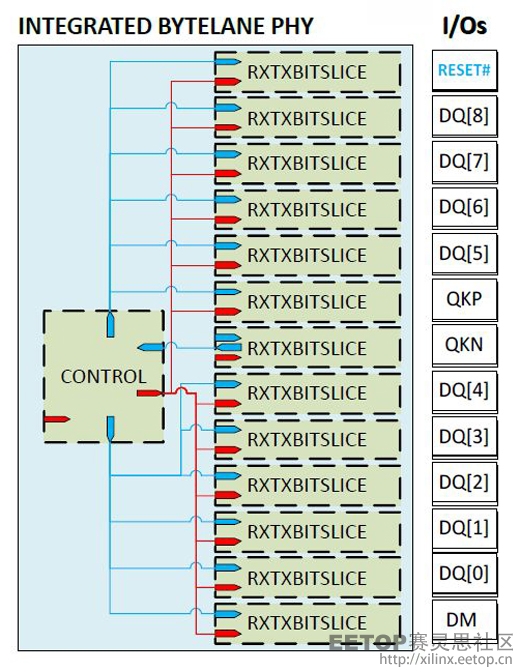

结果非常明显,I/O字节通道架构看来如此:

UltraScale FPGA I/O字节通道架构

逻辑上下一个问题也许是:“为什么13位?”简单的答案是,两个这样的库涵盖26位,这是DDR4 命令和地址行要求的。数据行、频闪和预选要求每个字节各另外添加11位,这符合新的13位UltraScale I/O库。. QDR和RL3 DRAM要求12个I/O行(9个数据行和2个时钟),这也符合13位块结构。任何余下的关键都可编程另作他用。

UltraScale FPGA的52管脚I/O库封装4个13位字节通道以及两个PLL和一个时钟模块,看似如此:

一个UltraScale 52管脚I\O库

两个PLL允许你将个库分开,这样就能在你的设计里为两个完全不同的目标服务。

关于更多的信息,你可在这里下载MemCon演讲的PDF

关于赛灵思UltraScale All Programmable FPGA更多的信息,点击这里。

你也许也想观看Adrian的关于该话题的视频,该视频展示了一款驱动DDR4-2400 SDRAM的以2500Mbps运行的UltraScale FPGA。见“Ready for DDR4-2400? Need the bandwidth? Need the lower power consumption? Watch this 8-minute video”,或者开始下面的视频。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Secrets-of-the-UltraScale-a...

© Copyright 2014 Xilinx Inc.

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网