作者:Adam Taylor

到现在为止,我们知道如何在基于Zynq SoC的系统中例化PicoBlaze 软核处理器。在这篇博客,我们将继续探索更多关于如何生成PicoBlaze 程序以及如何使用JTAG接口更新程序而不是重新编译整个设计。

显然,第一步我们要做的就是编写汇编程序实现我们要求的功能,我们可以使用PicoBlaze 或者更高级的IDE如fidex( http://www.fautronix.com/en/fidex )来编写程序。

这个汇编文件的后缀是.psm,PicoBlaze 处理器使用PicoBlaze 汇编器进行编译,关于PicoBlaze 汇编语法详细请看下载包内的UG129和All_kcpsm6_syntax.psm文件。这个语法非常简单易懂。

我们上周做的LED闪烁的例子使用的是下面的代码,该例子中PicoBlaze 处理器主频是40MHz,IO负载板的4个闪烁的LED闪烁频率是2HZ。我们通过一个向下计数的计数器来完成闪烁速率,先设一个预置的计数值,当递减到0时使LED状态翻转。

由于PicoBlaze 指令执行需要两个周期,所以我们先计算好预设值:

1. 5s / 50ns = 10,000,000 cycles

然而,看看下面的代码在循环延迟这里有五个指令需要执行,因此我们将上面计算的值除以5,于是得到一个常量等于2,000,000(十六进制为1E8480 )。

这就是最终在PicoBlaze 上跑的LED闪烁程序代码

NAMEREG s0,led ;rename S0 register to led

;As 8 bit processor we need four delay loops 256 * 256 * 256 * 256 = 4294967296

CONSTANT max1, 80 ;set delay

CONSTANT max2, 84 ;set delay

CONSTANT max3, 1e ;set delay

CONSTANT max4, 00 ;set delay

main: LOAD led, 00; load the led output register with 00

flash: XOR led, FF; xor the value in led register with FF i.e. toggle

OUTPUT led,01; output led register with port ID of 1

CALL delay_init; start delay

JUMP flash; loop back to beginning

delay_init: LOAD s4, max4;

LOAD s3, max3;

LOAD s2, max2;

LOAD s1, max1;

delay_loop: SUB s1, 1'd; subtract 1 decimal from s1

SUBCY s2, 0'd; carry subtraction

SUBCY s3, 0'd; carry subtraction

SUBCY s4, 0'd; carry subtraction

JUMP NZ, delay_loop;

RETURN

下一步就是使用下载包中的汇编器对源代码进行编译来生成一个存储文件(上周我们使用的FPGA用的是VHDL语言),一个日志文件,一个十六进制文件(.hex)。

写完这程序,我们打开上周的设计,并将其例化。尽管在联合测试时,如果我们需要改变程序的内容,其中一种方法就是使用JTAG下载器来烧录。JTAG下载器可以通过JTAG接口让我们修改PicoBlaze 处理器的RAM内容。然后我们可以测试这个更新的程序在我们重新编译FPGA配置之前,使用这个更新的程序,以至它可以再RAM中自动的运行。

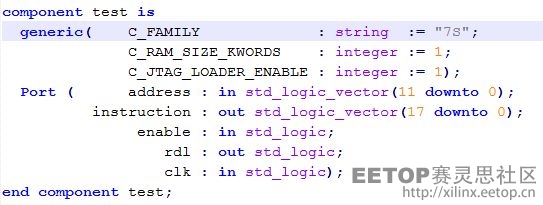

我们使用这个JTAG下载器只能对应一个PicoBlaze,如果一个设计有几个PicoBlaze (理论上是可行的),我们需要确保只有一个处理器使用JTAG下载器。我们通过在例化PicoBlze时将Generic 进行如下设置来实现:

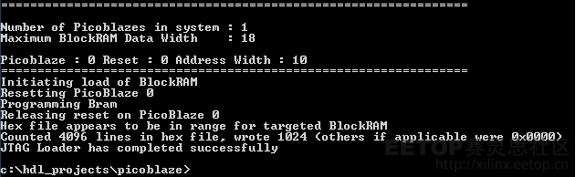

设置完JTAG下载器后,仅对应我们PicoBlaze 中的一个,我们然后使用JTAG下载器来烧录我们编译好的hex文件。

过程非常简单。首先根据你使用的操作系统从你下载的JTAG_loader文件夹选择正确的版本并拷贝到你的工作文件夹(你的hex所在的地方)。完成这步之后,你可以打开一个命令窗口然后定位到你的工作目录,并且使用下面的命令:

jtagloader –l .hex

注意,我已经为我操作系统对应的 jtagloader.exe的版本进行了重命名。

随着下载,你将看到JTAG下载器暂停了这个处理器的工作,并且在使处理器复位之前下载新的程序到内存,随后,你的新程序重新开始运行。

尽管这是一个非常强大的工具,它允许您下载并验证程序的修改,但不幸的是。它确实有几个缺陷。比如,

下一次你将这个板子上电的时候,还是执行原来的程序,而不是更新的那个,同时,在没有生成新的FPGA配置位流之前,你只能更新一个例化的PicoBlaze。

非常感谢这个Zynq架构使我们克服这些局限并且在接下来几篇博客我们将看到如何完成这些,这将非常令人兴奋!

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网