作者:Adam Taylor

本周的博客内容将继续学习Zynq SoC的XADC,上周一名读者提出了一个非常有意思的问题,我觉得有必要探究一下这个关于XADC的问题,也有必要中断一下正在进行的关于PicoBlaze处理器的学习讨论,这个问题解决之后我们将回来继续学习PicoBlaze。

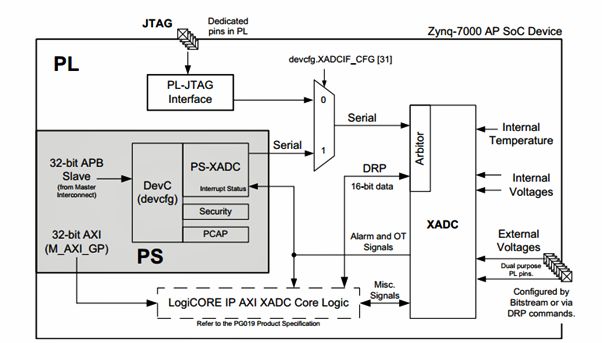

前面的博客中提到,有多种方式可以实现XADC与Zynq之间的交互,除了JTAG接口:

1.我们可以借助DevC接口实现XADC与PS(处理器系统)之间的直接交互,使用这种方式时,Zynq SoC的PL(可编程逻辑)部分不需要进行配置。然而使用这种方式连接时,主要用来检测内部器件的温度和电压,作为检测系统运行状态模块的一分部,例如串行接口的设计(复用了PL部分的JTAG端口)

2.使用XADC向导借助AXI总线接口与PS实现交互,主要是创建一个基于AXI总线的XADC DRP端口的封装包,这个接口主要是用来实现更高数据传输率的信号处理,信号采集来自外部外部的XADC接口,这个接口甚至能够支持AXI数据流式内部互联。

3.当然也可以在Zynq SoC的PL部分通过AXI总线接口实现XADC的内部交互,这种方式不需要与PS部分进行交互。例如你可以使用这个接口进行信号处理操作(滤波/FFT(快速傅里叶变换)等等)。

然而,当我们在PS部分使用XADC接口时,我们必须要解决一个问题:我们怎样配置这个期间来实现与AXI或者DevC接口的通信?

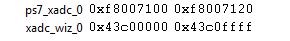

现在就让我们来解决这个问题,建立一个简单的Vivado工程,将XADC连接到一个PS部分的AXI主模式的端口,我们将建立的硬件信息导入到SDK,我们会在下图所示的文件中看到两个地址和驱动文件,我们将使用它们在SDK环境中访问XADC接口。

硬件XML文件中的XADC接口地址定义,使用与两个处理器内核(0和1):

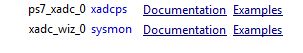

板级支持包MSS文件中提供的信息:

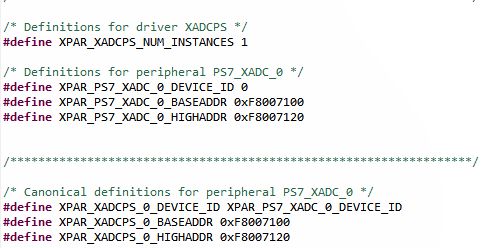

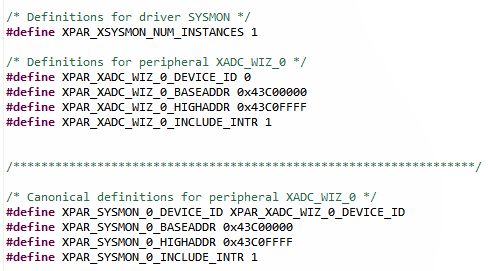

最后,在xparameters.h头文件中有关于7_XADC和XADC_WIZ的如下定义信息:

在板级支持包(BSP)的MSS文件中可以看到,我们使用不同的驱动通过不同的接口访问XADC,比如使用DevC接口,在BSP中提供的驱动是XADCPS.h,而使用AXI接口的驱动是XSysMon.h。

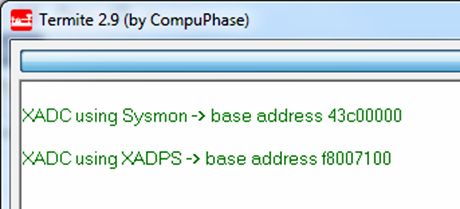

我们可以看出驱动通过读取配置指针设置的基地址来使用正确的交互接口,因此作为一个例子来检查每个驱动所使用接口,我已经创建了一个简单的应用,我同时使用了XADCPS和XSysMon驱动对指针进行了实例化和配置。每个实例化之后,代码都会读取配置指针来确定驱动所使用的基地址,然后确定所使用的接口方法。

上面的屏幕截图显示的是代码执行后,应用程序在终端窗口中输出的信息,可以确定我们可以从PS访问XADC使用上面两种不同的方式。

这篇博客的程序源代码已经上传到github存储库中:https://github.com/ATaylorCEngFIET/MicroZed-Chronicles 。在这个存储中我也修改了第8部分程序源码中的一个小错误。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网