作者:Adam Taylor

在本系列上一篇博客中,我们学习了解了使用XMD和XSDB来调试我们的应用和系统。然而为了确保我们的应用在性能上是优化的,另一个非常重要的方面就是对应用程序进行详细分析。

分析不同于调试,就分析功能而言,我们要使用SCU 定时器和中断来修改代码,完成在固定的间隔期间采样和记录应用程序的状态,这就允许我们确定被频繁调用的函数以及每个函数调用执行所占用的时间。知道了这些信息,可以帮助我们减少代码瓶颈,并确保系统性能满足要求。

对你的应用程序进行分析是非常简单的;然而不同于调试,一旦完成分析功能配置,这个应用程序必须执行完毕,这样才能收集到充足的数据。SDK 分析器采用GNU GProf工具。

为了确保对程序的分析我们需先完成下面两件事:

在板级支持包中开启分析功能支持

在应用工程中开启分析功能支持

在这篇博客中为了能够提供一个有意义的例子,我们需要一个足够复杂的应用来完成功能展示。因此,我使用了已有的HW和BSP定义,并创建了一个 Dhrystone模板应用,这样对我们的分析操作就足够的复杂了。(选择“File ->New ->Application Project”,键入工程名字,点击下一步,然后选择Dhrystone应用,完成)

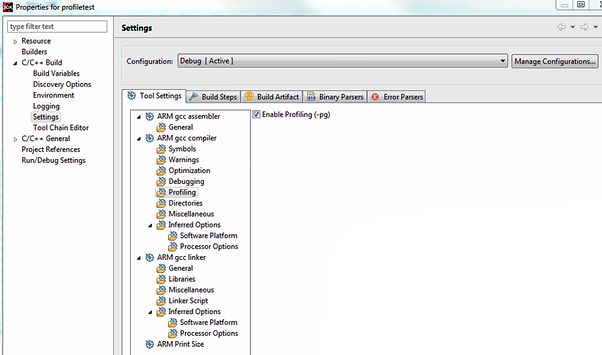

完成了应用工程的创建,下一步是使能应用的分析功能,在Dhrystone应用工程文件夹上右击,选择“C/C++ build

Settings”,进入到“Settings ->ARM gcc

Compiler”下拉菜单,选择“profiling”选项,在“enable profiling”前面的方框中打钩。

下一步是配置BSP的分析功能。我们需要对BSP和应用都正确的配置。在工程文件列表中选择BSP,右击,选择“Board Support

Package Settings”。在打开的BSP

设置菜单中选择“standalone”,然后使能“Enable_SW_Intrusive_Profiling”选项,保持“profile

timer”的设置为“none”,后面我们将会使用Zynq SCU定时器(这是在Zynq SoC上分析代码功能的仅有选项)。

配置BSP 的下一步是为分析功能设置合适的编译标志。在“driver”下拉菜单中选择“ps7_cortexa9_0”,在“extra compiler flag”选项后面的对话框中输出“-PG”。

现在我们可以关闭BSP设置,工具会重新生成BSP库文件,允许我们重新编译。

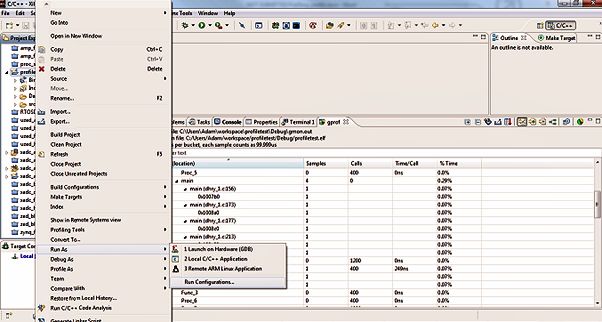

最后一步是配置应用的运行选项。与调试应用类似,我们需要借助JTAG来运行分析功能,同时获得分析数据。

打开“run configuration”选项卡,选择“Xilinx C/C++

application(GDB)”,然后选择已经存在的配置(如果这是一个新的工程,你需要重新创建新的配置)。选择你的配置文件,打开

“profile”选项卡,在“enable profiling”前面面打钩。

完成了前面所有的工作,我们的下一步就是运行这个应用,然后获取并分析数据,这些内容我们将在下一篇博客中介绍。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处