作者:Adam Taylor

在我最新一期发表的博客中介绍了如何通过Zynq PS(处理器系统)内部的AXI总线接口寻址Zynq SoC的XADC模块以及如何调试与分析你的应用程序。但是我们仍然没有看到Zynq SoC的一个非常有意思的方面,就是它能够将数据从PL(可编程逻辑)部分移动至存储器中——例如片上存储器或者DDR SDRAM,而存储器是映射到PS的地址空间上的。

作为工程师我们一直想这样做,将在Zynq PL部分实现的硬件存储器映射到PS部分的地址空间中,这是非常有用的,因为这样做可以允许采用PS部分的处理器对那部分存储器的数据处理进行分析。同时 PS部分的DMA驱动器将能够通过以太网接口和其他的I/O通道输出那部分存储器中的数据,并且使处理器的负载降到最低。

我们有两种方法可以选择:

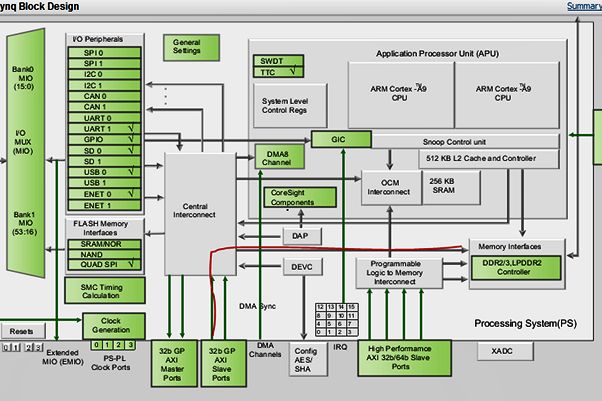

采用PL与PS之间通用的AXI端口可以访问PS DDR 存储器控制器,如下图中的红线所示。

这条红色线路连接通过了PS部分的Central Interconnect(中央内部互联)模块,因此这种方法可以让你访问外设I/O接口、Flash存储器接口,甚至PS部分主模式的AXI总线通用端口。

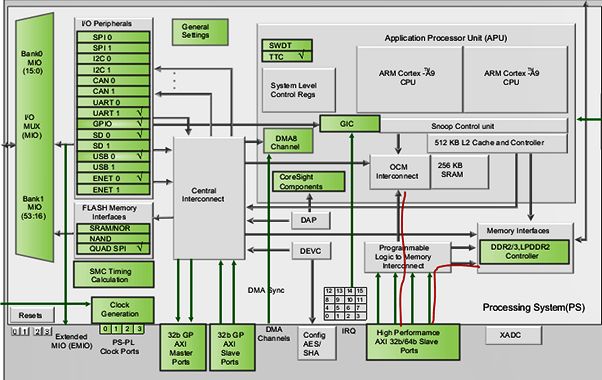

或者你也可以如下图红线所示的高性能AXI总线端口,这样你可以选择将数据存储到片上存储器空间或者通过SDRAM控制器将数据存储到外设的DDR SDRAM中。

所谓的“正确”选择取决于你需要传输的数据速率以及数据传输的目的地。下面的表格显示的是各种接口所能实现的最大数据传输速率:

无论你使用这两种方法中的哪一种,PS都会是从设备而PL会是主设备。这与以前看到的MicroZed系列中的例子是不一样的。

使用DMA将数据从Zynq 的PL转移到PS是很常见的,因为DMA传输可以保持吞吐量,同时保持处理器较低的利用率。(注:尽管AXI DMA控制器可能在PL部分实例化并且在数据传输期间充当主设备,但是仍然会有一个从模式的AXI4-lite端口供Zynq PS的处理器使用,来配置、启动和控制DMA的数据处理)

通常情况下,在Zynq PL中实例化的高性能核心将使用AXI streaming接口。AXI streaming没有地址通道,因此需要将其转换成具有存储器映射的AXI通道,才能用于将数据存储到存储器映射的地址中。完成这些工作的正常方法是在 Zynq PL中实例化AXI DMA模块,这个模块能够以AXI streaming数据流格式读出及写入数据。

接下的几期博客中我们将探索如何在Zynq 硬件中实现DMA模块以及必需的软件,在PL部分实例化一个模块,将模块的数据以AXI数据流的格式传输到DDR SDRAM中,DDR SDRAM是映射到PS存储空间上的,这样Zynq PS部分的ARM Cortex-A9 MPCore处理器就可以进一步处理这些数据。我们想这样做的一个非常好的例子就是能够测试ADC——确定它的SFDR(无杂散动态范围)和ENOB(有 效位数)——例如计算这些测量值帮助我们确保PCB(印制电路板)设计符合高速设计的要求。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处