VirtexTM-5 系列产品的推出,使得 Xilinx 公司再一次成为向 FPGA 客户提供新技术和能力的主导力量。过渡至 65 纳米工艺的 FPGA 具备采用更小尺寸工艺所带来的传统优势:低成本、高性能和更强的逻辑能力。尽管这些优势能够为高级系统设计带来激动人心的机会,但65纳米工艺节点本身也带来了新的挑战。

例如,在为产品选择 FPGA 时,功耗的考虑变得越来越重要。很可能下一代设计会需要在功耗预算不变(或更小)的情况下,集成更多的特性和实现更高的性能。

在本文中,我将分析功耗降低所带来的好处。还将介绍 Virtex-5 器件中所使用的多种技术和结构上的革新,它们能提供功耗最低的解决方案,并且不会在性能上有任何折扣。

降低功耗的好处

低功耗的 FPGA 设计所带来的优势不仅是能满足器件工作的散热要求。虽然满足元件指标对于性能和可靠性十分重要,但如何实现这一点对于系统成本和复杂性都有着巨大的影响。

首先,降低 FPGA 的功耗使你能够使用更便宜的电源,这样的电源使用的元件数量较少,并且占用的 PCB 面积也较小。高性能的电源系统的成本通常为每瓦0.5到1美元。低功耗的 FPGA 直接降低了系统的整体成本。

其次,由于功耗直接与散热相关,低功耗使你能够使用更简单、更便宜的热量管理解决方案。在很多情况下,设计者将不再需要散热器,或者只需要更小、更便宜的散热器。

最后,由于低功耗工作意味着更少的元件和更低的器件温度,因此将提高整个系统的可靠性。器件工作温度每降低10℃,就相当于元件寿命提高了两倍,因此对于需要高可靠性的系统而言,控制功耗和温度十分重要。

功耗:挑战和解决方案

FPGA (或任何半导体器件)中的总功耗等于静态功耗和动态功耗之和。静态功耗主要由晶体管的泄漏电流引起,即晶体管即使在逻辑上被关断时,从源极“泄漏”到漏极或通过栅氧“泄漏”的小电流。动态功耗是器件核心或 I/O 在开关过程中消耗的能量,与频率相关。

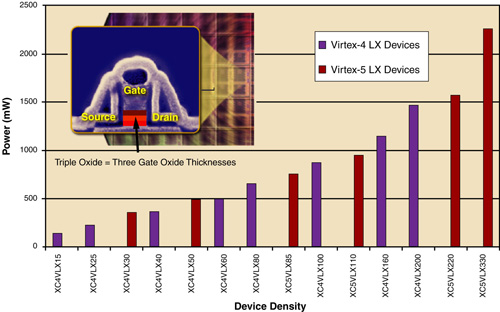

图1:85℃时的静态功耗比较

静态功耗

在缩小晶体管尺寸时(例如,从90纳米到65纳米),泄漏电流将会增大。新工艺结点所使用的短沟长和薄栅氧使电流更容易从晶体管的沟道区或通过栅氧泄漏。

在90纳米 Virtex-4 系列产品中,Xilinx 公司使用了“三栅极氧化层”的工艺技术,向 Xilinx 电路设计者提供了一种强有力的阻止漏电工具。在前几代 FPGA 中,使用两种栅氧厚度:薄栅氧用于 FPGA 核心中高性能、低工作电压的晶体管,而厚栅氧用于 I/O 模块中尺寸较大,需要承受大电压的晶体管。简单地来说,“三栅极氧化层”指增加一种中间厚度栅氧的晶体管,它的漏电比薄栅氧的核心晶体管要小得多。

“中间栅氧”的晶体管用在器件核心外围非关键性能的电路(像设置存储器)或不需要对变化的栅压进行快速开关响应的电路(像传输门)中。薄栅氧、漏电最大的晶体管只保留在需要快速开关速度的路径部分。结果,总的器件漏电被大大减小,同时性能仍能比上一代 FPGA 有很大提高。

三栅极氧化层工艺使 Virtex-4 器件比竞争性90纳米 FPGA 在静态功耗上平均减少了超过70%。这一结果非常成功,因此 Virtex-5 系列产品中大量使用了这一技术,在65纳米工艺结点上降低漏电。

虽然业界预测65纳米器件的静态功耗将会有大幅度提高,但是图1显示了三栅极氧化层工艺使65纳米 Virtex器件在最坏(温度最高)工作条件下达到了与尺寸相当的90纳米 Virtex-4器件相同水平的静态功耗。因此,Virtex-5 系列产品和竞争性高性能 FPGA 产品相比,在静态功耗方面具有真正的优势。

动态功耗

动态功耗为65纳米 FPGA带来一些其它方面的挑战。动态功耗的公式为:

动态功耗 = CV2f

其中C是结点开关时的电容,V是电源电压,f是开关频率。65纳米工艺节点使 FPGA 的逻辑能力和性能比传统器件有了显著提高,也就是说更多的结点工作在更高的频率上。如果其它方面的条件不变,动态功耗将会增大。

但是,对于65纳米工艺节点的动态功耗而言,也有一个好消息:FPGA 核心的电源电压(V)和结点电容(C)通常在每一代新工艺中都会下降,从而使得动态功耗比上一代 FPGA 有所下降。

Virtex-5 器件中,核心电源电压(VCCINT)从Virtex-4 中所使用的1.2V下降到1.0V。由于寄生电容变小(与更小的晶体管相关),以及逻辑块间的互联线长度变短、电容变小,使结点电容减小。此外,Virtex-5 器件在金属互联层之间使用了一种介电常数较低的材料。

Virtex-5 器件的平均结点电容比Virtex-4 器件大约减小了15%。加上电压降低带来的好处,至少相当于将 Virtex-5 器件的核心动态功耗降低了35-40%。

除“工艺尺寸缩小”到65纳米所带来的固有的35-40%的动态功耗降低外,Virtex-5 器件的架构创新,还能进一步降低每个设计的功耗。大多数可增加动态功耗有的结点电容,是由逻辑功能间的互连线引起的。新型 Virtex-5 架构在两个方面从根本上减小了连线电容:

Virtex-5的可配置逻辑模块(CLB) 是基于6输入查找表(6-LUT) 逻辑结构的,在以前的器件中是使用4输入查找表。这意味着在每个 LUT 中能够实现更多的逻辑,相当于较少的逻辑级,从而降低了对逻辑功能之间大电容连线的需求。

Virtex-5 的互联结构目前包括了对角线对称的连线,意味着每个 CLB 与所有相邻的模块(包括处于对角线位置的模块)之间都有直接的“单一”连接。当逻辑功能之间需要连接时,这一连接更有可能成为总电容最小的“单一”连接,而以往的互联结构对于相同的连接问题可能会需要两个或更多结点。

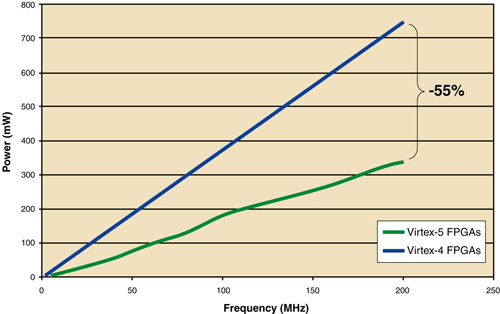

图2: 计数器标准设计的动态功耗比较

6-LUT 结构和改进的互联模式,通过降低平均结点电容来降低核心的动态功耗,效果远远超过仅使用65纳米工艺所带来的改进。图2显示了来自标准设计的核心动态功耗的测量结果,其中每个 Virtex-5 器件和 Virtex-4 器件中都有1024个8位计数器。这些实际的测量结果显示,工艺和结构上的共同优化所带来的动态功耗的降低超过了50%。

硬IP模块

Virtex-5器件中包含的硬IP模块(专门用来实现一些常用功能的电路)的数量,超过业界其他任何一款 FPGA。相比使用通用 FPGA 逻辑而言,使用搭载这些模块的 FPGA 设计来实现这些功能,可进一步降低功耗。

与 FPGA 结构不同,这些专用的模块中只有实现所要求的功能必需的晶体管。并且没有可编程的互联,因此互联电容最小。较少的晶体管和较小的结点电容能降低静态和动态功耗。从而使这些专用模块在实现相同功能的同时,功耗只有使用通用 FPGA 结构的十分之一。

除增加新型的专用模块外,Virtex-4 器件中融合的很多模块,在 Virtex-5 器件中都被重新设计,以增加新的特性,提高性能,降低功耗。例如,Virtex-4 系列中18-Kb 的 block RAM 存储器在 Virtex-5 器件中被增加到了36-Kb;每个 block RAM 能被分成两个独立的 18-Kb 的存储器,以便向下兼容 Virtex-4 的设计。

有趣的是,从功耗的角度来看,每个 18-Kb 的子模块由两个 9-Kb 的物理存储阵列构成。对于大多数的 block RAM 配置,任何对于 block RAM的读写请求一次只需要访问 9-Kb 物理存储器中的一个。因此其余的 9-Kb 存储器能在不被访问时被有效地“关断”。在过渡至65纳米工艺所带来的功耗降低的基础上,这种结构又使功耗进一步降低了50%。这一对于9-kB 模块的“乒乓”访问是新的 block RAM结构所固有的,这就意味着使用这项功能不需要用户或软件来进行控制。它能动态并自动地进行,使所有使用 block RAM的设计降低了大量的功耗,并且不会影响模块的性能。

Virtex-5 器件中专用的 DSP 元件也进行了大量的改进,以实现更多的功能,提高性能,并降低功耗。在片与片的比较中,新型的 Virtex-5 DSP 片的功耗比 Virtex-4 DSP 片的功耗降低了大约40%。这主要归功于前面所讨论的65纳米工艺中电压和电容的减小。

然而,由于 Virtex-5 DSP 片具有更强的功能和更广泛的接口,许多 DSP 运算通过利用这些附加的功能进一步降低了功耗。在许多情况下,当使用新型 DSP 片的全部功能时,总功耗最高可降低75%。请记住即使你不是在设计一个 DSP 产品,也能使用 DSP 片来实现标准的逻辑功能(计数器、加法器、桶式移位器),这样会比在标准 FPGA 逻辑中实现同样的功能节省功耗。

最后介绍的经过改进的专用模块是 Virtex-5 系列的 LXT 平台,其中包括了几吉位的串行收发机,能以高达 3.125Gbps 的速率工作。这些 “SERDES” 模块在实现时着重考虑了低功耗需求。每个 Virtex-5 LXT 器件中的全双工收发机在 3.125Gbps 的速度下的总功耗小于100毫瓦,与Virtex-4串行收发机相比降低了大约75%。

图3:典型设计中现有 FPGA 的功耗比较

结论

Xilinx 公司悠久的创新历史能够追溯到20多年前第一块 FPGA 的发明。因此 Xilinx 公司理所当然地成为第一家在深亚微米技术中将降低功耗作为首要任务的公司。与 Virtex-4 系列产品一样,Virtex-5 器件也采用了一系列工艺和架构上的革新,力求在提供尽可能低的功耗的同时,仍然使性能提高30%或更多。

如图3所示,Virtex-5系列产品的静态功耗与 Virtex-4 器件相当,但比竞争性 FPGA 具有明显的优势。作为唯一的65纳米 FPGA,Virtex-5 器件核心的动态功耗比市场上其它高性能 FPGA 低至少35-40%。像新型 6-LUT 和对角线对称的互联等架构上的革新,使实际核心动态功耗进一步降低了50%或以上。此外,利用数量空前的专用模块进一步降低了功耗。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网