作者:Steve Leibson, 赛灵思战略营销与业务规划总监

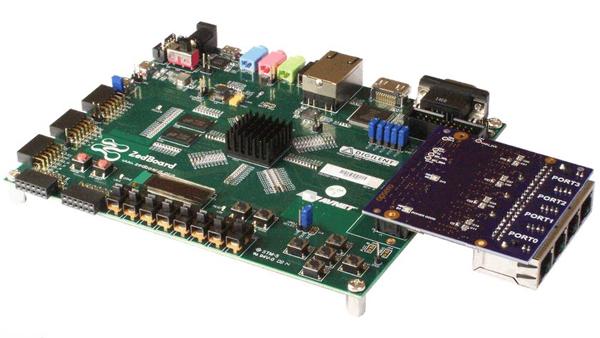

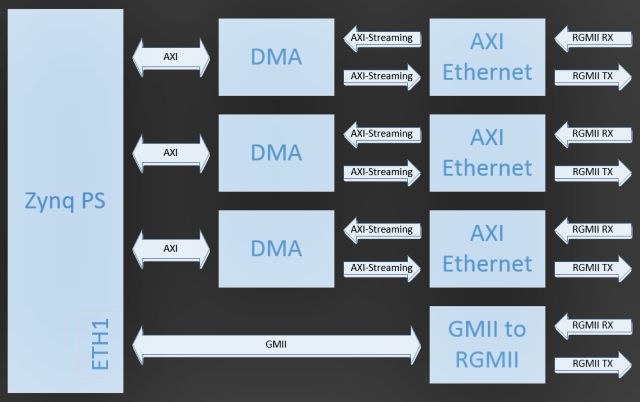

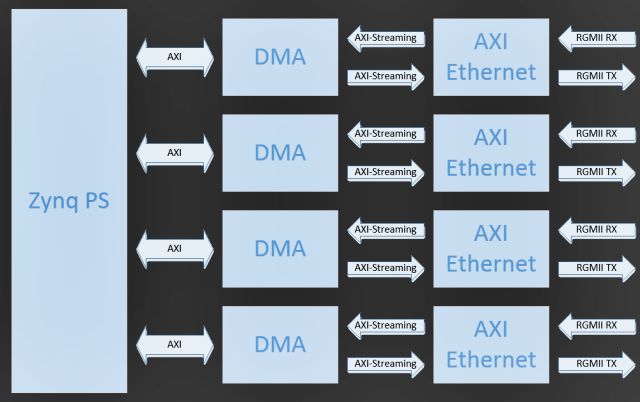

来自Opsero ElectronicDesign的以太网FMC卡接入基于 Zynq的 Avnet ZedBoard的LPC(低引脚数)FMC连接器,在板子的外设上添加了4个千兆以太网端口。板子本身有4个Marvell 88E1510千兆以太网PHY和带有集成磁件的端口连接器。以太网MAC位于ZynqSoC,使用ZynqSoC的PS(处理器系统)的硬件以太网MAC,或者在ZynqSoC的PL(可编程逻辑)中例化的以太网MAC。Opsero为这两种用法提供了参考设计,见下面的框图:

Opsero由Jeff Johnson建立。这是一座FPGA设计室,Johnson决定创建标准的产品供应。如果你使用赛灵思ZynqSoC或者赛灵思Vivado设计套件,你也许乐意阅读Johnson的博客fpgadeveloper.com.

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Quad-Gigabit-Ethernet-FMC-b...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网