来自赛灵思的Adrian Cosoroaba和Terry Magee在圣克拉拉会议中心的Memcon 中发表了关于“高性能DDR4接口和FPGA灵活性”的主题演讲。赛灵思首席工程师Magee,设计了用于新赛灵思UltraScale All Programmable FPGA的DDR4-2400 PHY架构,演讲会讨论赛灵思PHY设计团队怎么样将可靠的DDR4-2400内存接口和可编程FPGA I/O引脚极高的灵活性(与ASIC相比)且低功耗想结合。

DDR-2400需要的性能增加了,但并没有降低I/O引脚的运行其他任务的性能,照样以高速串行I/O端口运行或者作为LED驱动。此外,相同的高速PHY也可以用来驱动DDR3-2133,DDR3L-1866和LPDDR3 SDRAM;low-latency RLDRAM 3和 QDRII+ and QDR IV SRAM。这对单个I/O引脚来说是艰巨的,这就关系的到FPGA PHY设计者期望性能和灵活性的怎样排序

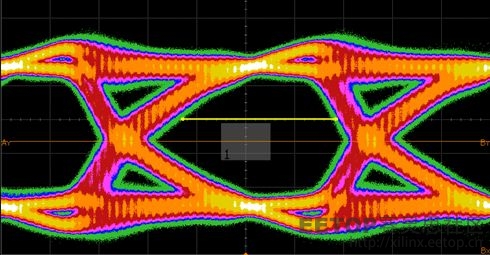

开发DDR4-2400 PHY的解决方案开头就碰到问题,从演示稿中偷走了一行。我会告诉你这不是想购买第三方PHY IP然后放入你的设计中这么简单。可以看看这个图片

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Open-Eye-How-do-you-design-...

©Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网