作者:Steve Leibson, 赛灵思战略营销与业务规划总监

系统内部连接是个大问题。问题随着系统越复杂而变得越严重——复杂的逻辑块连在一起,内部连接也跟着变复杂。当FPGA变大时(大到足以承担整个系统),内部连接的复杂度也增加。在简单系统中,点到点的直线连接显然是最有效的。而在大系统中,总线(当他们在芯片上时看似是一个大型复用系统)将是更好的选择。系统变得更复杂时,你可能需要交叉的内部连接。最后,真正复杂的系统甚至还需要片上网络来提供系统内部连接,另外还需要考虑带宽和延时。你如何从中选择?这些就不能自动完成吗?

这不是个“新”问题。这是我2006年写的书“Designing SoCs with Configured Cores”中关于这个话题的文章:

“如果上千年的土木结构经验开发了一种按钮的方式来桥接设计,那么很可能只有一种基础类型的桥接——概念桥接FPGA,如果你愿意这么叫的话。然而,事实上现在不仅仅只有一种基础桥接类型,还有:”

1. 梁架式

2. 桁架式

3. 刚架式

4. 拱门式

5. 斜拉桥式

6. 悬挂式

“桥梁建筑师也结合基本桥梁类型来建造复合桥梁。例如,旧金山金门大桥的主桥就是悬挂桥梁,但是引桥有拱门和桁架桥的成分。”

“SoC设计师需要严谨的方式来评价不同的架构和精确的方法来实现所选的架构,并不需要手动翻译和实现那些复杂的且只有人类能懂的规范。”

九年后的今天,正如大约十年前在这章节中所展望的一样,赛灵思今天推出了内部连接设计自动化。

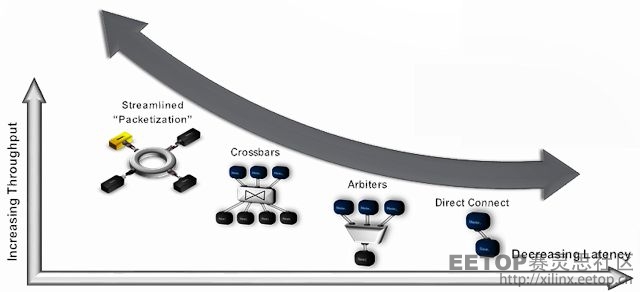

SmartConnect是一个全新的创新型的方法,使你能在全新Xilinx UltraScale+ FPGA和MPSoC上实现复杂系统的片上内部连接最优化。这款工具为你提供了20%到30%的系统级性能提升,同时减少了芯片的空间和功耗。SmartConnect应用内部连接拓扑最优化来满足设计规定的吞吐量和延时需要,同时减少内部连接逻辑的空间。它通过分析设计的IP接口和连接性,观察整个系统(不仅仅是单个IP块的集合),选择若干个备选内部连接拓扑,然后做出智能的最优化来消除过量的逻辑并避免拥塞和膨胀。

下图概念性的展示了智能连接选择满足吞吐量和延时需要的连接,同时最小化空间和功耗。

SmartConnect也可以智能地、自动地桥接不同接口类型——就像视频流连接内存——使用简单的拖放GUI。

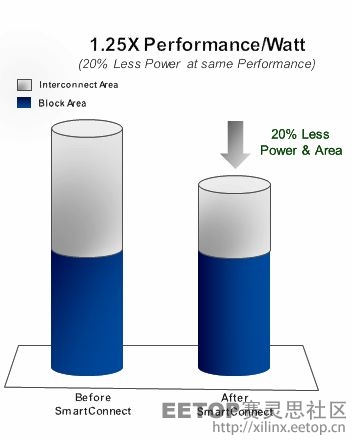

所以,这个魔术行得通吗?这是真正系统级设计的例子:

在这个例子里,内部连接大概消耗了原来设计空间的一半。这在复杂系统设计中并不是一个典型。在使用了SmartConnect后,消耗了相同数量空间的逻辑(当然),但是内部连接消耗了更少的空间,减少了20%的功耗。系统性能/功耗净提升了25%。

这是一项真正值得你考虑的技术。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/SmartConnect-Interconnect-d...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网