2月底,Xilinx发布了下一代16nm产品特点的新闻:《Xilinx凭借新型存储器、3D-on-3D 和多处理SoC技术在16nm继续遥遥领先》(http://www.eepw.com.cn/article/270122.htm),大意是说,Xilinx新的16nm FPGA和SoC中,将会采用新型存储器UltraRAM, 3D晶体管(FinFET)和3D封装,Zynq会出多处理器产品MPSoC,因此继28nm和20nm之后,继续在行业中保持领先,打破了业内这样的规则:Xilinx和竞争对手在工艺上交替领先。

本文引用地址:http://www.eepw.com.cn/article/270775.htm

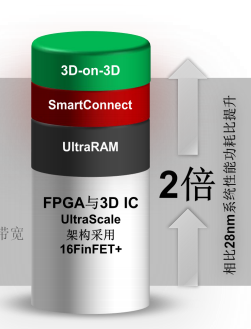

图 Xilinx 16nm产品具备的主要功能

为何此时宣布2年后的新产品?

人们不免产生这样的疑问,2014年12月,Xilinx的20nm芯片刚刚量产。为何Xilinx又如此之快地宣布两年后将会量产的16nm计划?答案是:你懂的!Xilinx的竞争对手Altera二三年年前已宣布和Intel进行战略合作,Altera的14nm 3D(Trigate)芯片将由Intel代工。当时Xilinx的代工厂——台积电的技术(16FF)还无法和Intel匹敌。这次,代工厂台积电推出了16FF+新工艺,Xilinx的腰板一下子硬了。

当然,仅仅靠代工厂也显得太low了,在上一次20nm+UltraScale组合的成功基础上,Xilinx又推出了前述的多种猛料,并抛出了16nm的UltraScale+、SmartConnect等料。

另外,Xilinx的销售策略也改变了,多种制程的产品将在市场上共存,这也是Xilinx不吝公布16nm的下一代产品。Xilinx公司全球高级副总裁兼亚太区执行总裁汤立人(下图)称,由于16nm产品太复杂了,不是所有应用都会用到,因此不会对20nm、28nm的产品产生冲击,各种制程的产品会在市场共存,以满足复杂度不同的各种应用。但在过去,从90nm推出到65nm的时候,Xilinx就不去卖90nm了;当40nm出来后,就不推65nm了。

猛料1:3D-on-3D

16nm的3D-on-3D,即3D晶体管(FinFET)和3D封装,据称是在半导体公司里第一家实现的。

其实早在28nm时,Xilinx就已推出了3D封装。汤立人称3D IC受到很多做ASIC仿真的通信大公司的欢迎。

Xilinx在20nm时的3D IC实现了400万逻辑单元,共有190亿个晶体管,价格十几万美元,听起来好像贵得吓人,但是如果换成做ASIC,数千万美元才能搞定,而且ASIC不能修改,风险非常大。

3D-on-3D的好处是集成度和成本。集成度提高不言而喻。从成本来说,Xilinx可以做到更低的系统成本,做3D IC要比单芯片的3D便宜非常多。

FinFET主要靠台积电的工艺搞定。

3D封装最大的挑战是散热,尤其是中间那层的散热问题。市面上大部分3D堆叠封装产品是存储器,因为存储器不是经常存取的,耗能较少。但是FPGA/SoC由于要做运算,能耗较大。Xilinx的做法是,上下层是有效电路,这是晶体管要跑的,有功耗的,中间是金属介质层,主要用于连接信号,没有晶体管,因此就没有耗电和热的问题。(笔者注:由于中间层没有晶体管,业界也有人认为这是2.5D封装)。

猛料2:软件成为UltraScale+的重要部分

UltraScale+有Virtex,Kintex和Zynq。工艺方面主要是3D-on-3D。

图 UltraScale+产品组合及价值

此时,Xilinx更强调了Vivado和SDx(软件定义的系列工具)软件工具的作用。因为Xilinx的CEO Moshe Gavrielov过去是著名的EDA(电子设计自动化)公司——Cadence的副总,他改变了Xilinx的业务模式,想转型成为EDA公司(笔者注:业界一些媒体评论认为),因为工具是非常重要的,工程师要想成功地设计,应该完全靠工具,和硅芯片没太大关系。理由是:现在FPGA越做越复杂,但主要还是硬件工程师用FPGA,软件工程师做不了FPGA设计。现在大学生很多喜欢做软件工程师,硬件工程师越来越少。所以,Xilinx想要扩大市场,必须花很多功夫来吸引软件工程师。为此,在北京,Xilinx前两年研发了HLS,在某些应用中可以用C语言做FPGA设计。Xilinx也越来越多地提SDx方面的事情。

猛料3:UltraScale+使性能功耗比提高2~5倍

怎么达到2倍到5倍的系统性能呢?汤立人称,16nm加上3D 封装和FinFET,而且嵌入了很多的存储器(UltraRAM),还有新一代的智能互联(SmartConnect)。

在工艺上,Xilinx与台积电合作,之前台积电有16FF,16FF比Intel、三星的14nm差一点,后来台积电又推出了16FF+,比16FF性能提高15%,在功耗方面降低大概30%,与Intel的14nm工艺相当。

一个产品成功与否,不光是看工艺的,与架构关系也很大。Xilinx第一个提出ASIC级的可编程架构UltraScale,16nm时将升级到UltraScale+。

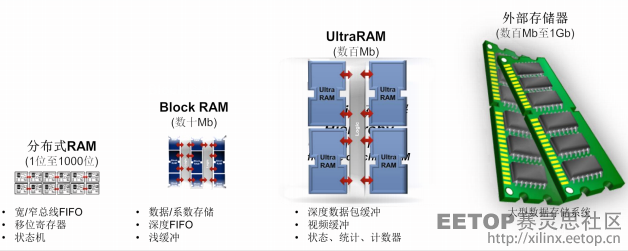

猛料4:UltraRAM

UltraRAM是最新的存储器技术,是台积电与Xilinx共同开发的。Xilinx认为该技术主要适合视频应用。众所周知,分布式RAM可以达到1000位,Block RAM可以达到数十Mb,如果应用需要比较大的存储器的话,以前在UltraScale+之前,用户需要很多外部存储器,但是当布置大量的外部存储器的时候,很多信号、性能等方面的问题会出现,造成性能降低、功耗提高很多,因为要驱动外部信号。

因此Xilinx的UltraScale+中加入了UltraRAM,使容量可以达到432Mb,可以做到深度数据包缓冲、视频缓冲,这非常有用,因为在4K/8K视频应用方面缓存至关重要。

在芯片内做RAM的好处是:信号不需要在芯片和芯片之间传输,所以无论在功耗、性能、成本上都会大大提升。

猛料5:SmartConnect降低功耗20%

另一个与20nm不同的地方在于,Xilinx现在的软件可以根据延迟决定信号放在哪一种互联里。因为Xilinx的产品有不同的互联设计在里面。以前软件没有这么规律地去优化究竟什么信号、block放在互联里面,所以在性能和功耗方面不是最优化的。

SmartConnect是Xilinx内部开发的一个工具,可使功耗降低20%左右。

猛料6:多处理器MPSoC

Xilinx向嵌入式领域进军的代表作是Zynq,有两个ARM Cortex-M9核,已经应用于汽车、医疗、工业等方面。在国内,比如点钞机会用很多这种技术,Zynq,不光是点,还可以验证钱币的真假,因为图像处理功能很强。

现在Xilinx推出MPSoC——多处理SoC,即用合适的引擎来做合适的事。通过MPSoC可使性能提高5倍。

MPSoC的内容很多,有四核的A53,是64位核心。还有32位双核的实时处理器,有非常多的图形处理器(采用ARM Mail-400M系列),还有视频编/解码器,因为4K/8K需要编解码。以前是用软的方法来做编解码,现在是用硬的方法来做,性能会提升很多。加上Fabric,UltraRAM,还有混合模拟信号。

在这么多内容在里面,功耗很重要。如果不需要用所有功能,MPSoC可以将部分的电源功耗降低或者关闭。另外,要做到保密、安全、可靠。

16nm的应用展望

在无线方面,在4G/LTE方面Xilinx做得非常成功。接下来的16nm将做LTE-A,5G也快来了。在国内很大的一家客户已经在用20nm芯片了,他们也准备要用16nm做LTE-A。

4K/8K视频需要很多缓冲方面的技术,现在20nm可能实现得不够好。在数据中心,也可以有非常多的应用。在物联网方面也是,机器到机器,所以在FPGA的应用非常非常多,OTN等方面。

Xilinx在通信方面,占了一大半的市场份额,其实Xilinx一大半都是在通信以外的应用,在汽车、医疗、工业、通信等方面,Xilinx一直会扩张。

出货时间表

预计今年第二季度会推出16nm首款流片,提供给早期介入的客户。2015年第四季度会有样片。如果要量产的话还需要两年左右的时间。

小结

Xilinx的16nm产品推出了一系列组合拳,逻辑、处理、存储、模拟,高集成、低功耗,功能可谓强大。不仅如此,Xilinx还希望通过软件工具来吸引更多的软件人员,以达到这样的境界:只管用工具来设计,至于是神马芯片并不重要。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网