By Adam Taylor

之前在博客发表的文章中,我已经介绍了在Vivado环境下的基本约束,这篇文章将着重介绍时序约束。

在FPGA里的底层,我们利用时钟来提供的时序参考,据此来传输和接收数据。如果我们想要对时钟进行分析,我们需要考虑时钟周期,建立时间(Tsu)和保持(Thd)时间,和Tclk-Q,并要保证他们的时序没有冲突。

尽管我们可以手工检查某一个寄存器的时序,但对于包含数百万触发器和非理想时钟树的复杂的设计来说,手工检查是不可能的。因此必须依靠EDA工具(本例中为Vivado设计套件)来自动处理时钟的抖动和偏移。

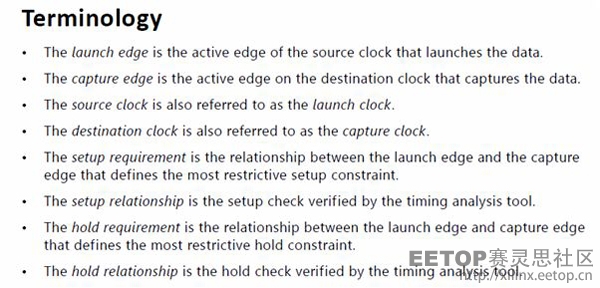

为了理解Vivado环境下的时序约束,我们必须理解用来约束的相关术语,这部门在Vivado Design Suite User Guide: Using Constraints中有更详细的介绍。

术语

上述这些术语可以帮助我们理解和定义FPGA设计的时序行为。

在我们考虑怎么定义这些约束之前,我觉得有必要具体的解释一下什么是建立和保持条件。其他的术语看起来都很直观,很好理解。

这个建立时间定义了在下一个时间沿出现前,寄存器里的数据必须保持稳定不变的时间。注意到,此时我们可能正在处理多个时钟。发射时钟和发射数据源相关联。捕获时钟和捕获数据的目的触发器相关联。建立要求等于时钟的捕捉边沿时间减去发射边沿时间。注意:这些时钟可能不一样——它们可能有不用的相位或者不同的时钟周期。如果使用了不同的发射和捕获时间,那么当你考虑两个时钟间最坏的关系时,建立条件取这两时钟中较小的那一个。

保持时间是指在捕获了时钟沿后数据必须保持稳定不变的时间。这个保持时间是当前捕获沿减去下一个发射沿的较大者。如果发射和捕获时间不一样,那么必须考虑时钟间最糟糕情况下的时序。

Vivado可以分析建立和保持时间,并且提供这些分析的结果。结果报告显示了设计松弛度。正的松弛度意味着在寄存器有错误的值和趋于稳定时,定时器将不会计时。负的松弛度意味着由于时序冲突,这时稳定度是个问题。

当然为了进行时序分析,我们需要定义时钟以及提供包含合适设计信息的设计工具。为了在XDC(Xilinx Design Constraints赛灵思设计约束)中定义一个时钟,我们需要提供最基本的定义。

对于时钟,Vivado包含了三种概念,它们之间的定义稍微的差别。

利用下面的命令来生成主时钟和虚拟时钟:

create_clock –period –name –waveform [source objects]

例如,如果想在一个输入管脚上定义一个10纳秒输入、占空比为50%的时钟,我们可以用下面这行命令:

create_clock – period 10ns –name sys_clk –waveform {0 5} [get_ports sys_clk]

这个行命令中有意思的地方是“–waveform {0 5}”,它用来限定波形沿的跳变点在0和5纳秒,因此10ns的时钟,占空比为50%。如果想要设计不同占空比的波形,比如30:70,我们可以用“–waveform {3 10}”。(注:此时跳变点为3ns和10ns,因此占空比为30%)

利用下面这个命令生成产生时钟:

create_generated_clock –name –source –edges –divide_by –multiply_by –duty_cycle –edge_shift –master_clk –combinatorial

例如为了产生2分频的时钟,我们可以用如下命令:

create_generated_clock –name clk_div2 –divide_by 2 –source [get_ports sys_clk] [get_pins divider_out]

在下一期博客中,将依旧研究时序约束,例如时钟组,不确定性和异常。

点击这里,你可以访问到MicroZed开发板笔记之前的部分。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

©Copyright 2014 Xilinx Inc

如需转载,请注明出处