By Adam Taylor

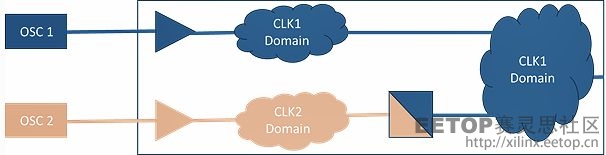

在之前的博客中介绍了Vivado的基本时序约束,时序约束定义了系统频率或自己所定义的时钟频率。为建立良好的时序约束,下一步是需要建立时钟路径之间关系的定义。这样,Vivado 就可以通过分析各个时钟路径之间的关系,来确定是否需要对这些路径进行优化。默认情况下,Vivado 分析所有内部信号的时序关系。然而,Vivado并不能够准确的分析出一个设计中所有路径的时序关系。比如说,异步时钟之间的相位关系,不能准确地确定。因为根据定义,他们是异步的。

在Vivado中,我们可以通过约束文件来定义时钟路径的关系和声明时钟组。在以声明的时钟组中,Vivado不执行时序分析。

Vivado定义了以下三种时钟:

同步时钟——同步时钟有一个可预测的时序/相位关系。他通常来自系统主时钟或主时钟产生的时钟,它们共享同一个的根时钟,因此有一个共同的周期。

异步时钟——异步时钟没有可预见的时序/相位关系,这主要是因为有不同的主时钟(和这些主时钟生成的子时钟)。异步时钟具有不同的根时钟。

不可扩展的时钟——两个时钟的公共周期超过1000个时钟周期还没被确定,那么这两个时钟是不可扩展的。如果不能建立一个共同的时钟周期,那么Vivade就会通过用1000个时钟周期这种最糟糕的情况来建立关系。然而,不能保证这种关系能真实地代表事实上最糟糕的情况。通过已提供的情况这只是Vivade所能做的最好的估计了。

我们可以使用Vivado的时序报告,来帮助我们确定异步和不可扩展的时钟

一旦我们确定了异步时钟,我们就使用set_clock_groups约束去禁用它们之间的时序分析。Vivado采用SDC为基础的约束,我们使用下面的命令来定义时钟组。

-name是时钟组的名称。-group选项允许你定义时钟组的成员(没有时序关系的时钟)。当选择多个时钟源之一去驱动一个时钟树(例如BUFGMUX或BUFGCTL)时,你可以使用-logically_exclusive和-physically_exclusive选项。这样的时钟是相互排斥的,并且不可以同时存在于时钟树中,因此我们不希望Vivado来分析这些时钟之间的关系。-asynchronousoption定义了异步时钟路径。

最后,你需要考虑时钟的不理想关系,特别是,这意味着抖动。你将需要解决两种抖动:输入抖动和系统抖动。输入抖动存在于当他们进入你的系统时的主时钟输入。当过渡时期实际发生时与当它在理想条件下应该发生时,他们之间的抖动是不同的。系统抖动来自于设计内的噪声。我们可以使用Vivado的set_input_jitter约束来定义每个主输入时钟的抖动。系统的抖动被设置用于使用set_system_jitter约束时的整个设计中。

在这一点上,我们的约束项包含:

●对于输入时钟的主时钟约束。

●相对于该主时钟产生的子时钟的关系。

●我们不想分析的异步时钟间的时钟组。

●任何专属时钟的时钟组。

●对于每个主时钟的输入抖动的定义。

●对整体设计的系统的抖动定义。

在完整的设计中已经定义了每个时钟树的约束后,我们然后可以开始观察时钟树内的时序异常。比如,下一篇博客将会着眼于多周期路径。关于时钟组的最后一点:时钟组之间数据传递需要正确的分析,以确保时钟域之间的重新同步和正确的数据传输。这里的目标是避免亚稳态问题。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网