赛灵思Zynq-7000全可编程 SoC的众多优势之一就是拥有两个ARM Cortex-A9板载处理器。不过,很多裸机应用和更为简单的操作系统只使用Zynq SoC处理系统(PS)中两个ARM内核中的一个,这种设计方案可能会限制系统性能。

根据所开发的应用类型不同,可能需要这两个处理器都运行裸机应用,或者需要在每个处理器上运行不同的操作系统。例如,其中一个处理器执行关键计算任务,从而运行裸机/RTOS应用,同时第二个处理器通过Linux提供HMI和通信功能。

什么是多处理?

这两种方案都属于多处理。简单定义:多处理就是在一个系统中使用一个以上的处理器。多处理架构可允许一次执行多个指令,但并非必须如此。

多核处理包括两种类型:对称和非对称。

对称多处理是通过将负载分配给多个内核,从而能够同时运行多个软件任务。而非对称多处理(AMP)则是使用专用处理器,或者针对特定应用或任务在相同处理器上执行应用。

根据定义,使用Zynq SoC上的两个内核执行裸机应用或不同操作系统都属于非对称多处理。Zynq SoC上的AMP可能涉及如下几种组合:

• 在内核0和内核1上运行不同操作系统;

• 在内核0上运行操作系统,在内核1上运行裸机应用(反之亦然);

• 在两个内核上均运行裸机应用,执行不同程序。

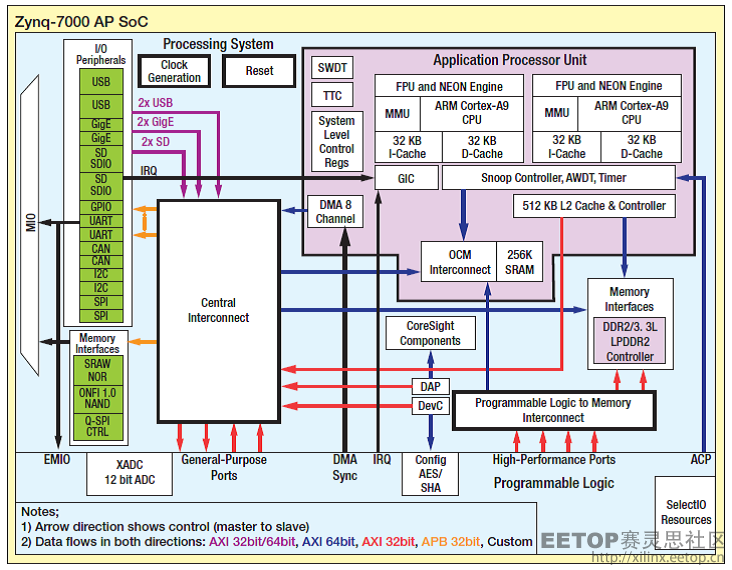

当您决定在Zynq SoC上创建AMP系统时必须考虑一个实际问题,即ARM处理器内核同时包含必须进行正确寻址的私有资源和共享资源。这两个处理器都有私有的L1指令和数 据高速缓存、定时器、监视时钟以及中断控制器(针对共享和私有中断)。另外还存在一些共享资源,常见的有I/O外设、片上存储器、中断控制器分配器、L2 高速缓存和位于DDR存储器中的系统内存(见图1)。这些私有和共享资源均需要精心管理。

每个PS核都有自己的中断控制器,能够利用软件中断实现自身与一个或两个内核的中断。这些中断通过ARM的分布式中断控制器技术完成分配。

由于针对每个内核执行的程序都位于DDR存储器内,因此您必须特别注意以确保对这些应用进行正确分割。

建立AMP

建立AMP并使其运行在Zynq SoC上所需的关键因素是引导载入程序,该程序会在第一个应用载入到存储器后寻找第二个可执行文件。赛灵思在XAPP1079中提供了有用的应用指南和源 代码。该文档包含修改后的第一阶段引导载入程序(FSBL)和独立OS,可用来创建AMP系统。

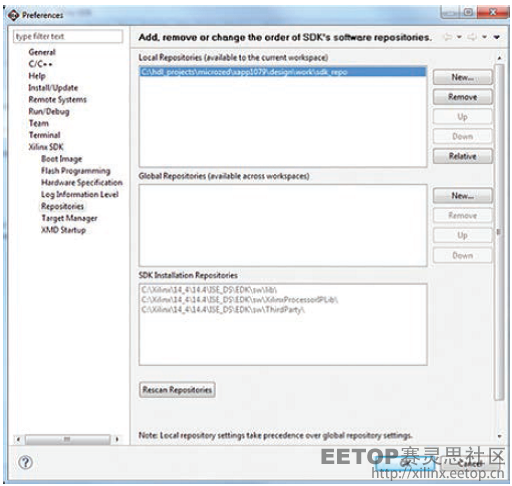

首先要做的是下载与应用说明配套提供的ZIP文件,再将FSBL和OS这两个要素解压到期望的工作目录。然后,必须给名为SRC“design”的 文件夹重新命名。现在,非常重要的一点是一定要确保软件开发套件(SDK)知道这些新文件(修改后的FSBL和独立OS,两者兼备)的存在。因此,下一步 需要更新您的SDK库,以便使其知道这些新文件的存在。

使用软件中断与硬件中断基本相似,区别只在于您如何触发它们。

这很容易实现。在SDK中赛灵思工具菜单下选择“库”,然后选择“新建”,随之导航到目录位置<您的工作目录>\ app1079\design\work\sdk_repo,如图2所示。

处理器间的通信

为AMP设计创建应用之前,您需要考虑应用如何进行通信(如有需要)。最简单的方法是使用片上存储器。Zynq SoC配备256KB的片上SRAM,可从以下四个源地址进行访问:

• 利用侦测控制单元(SCU)从任意内核进行访问;

• 利用SCU通过AXI加速器一致性端口(ACP)从可编程逻辑进行访问;

• 利用片上存储器(OCM)互联通过高性能AXI端口从可编程逻辑进行访问;

• 也是利用OCM从中央互联进行访问。

图1 – Zynq SoC处理系统,显示私有和共享资源

图2 — 将您的新文件添加到库

由于这些不同的访问源都能对片上存储器进行读写,因此尤为重要的一点是,在使用OCM之前一定要首先详细了解其的运行方式。

既然OCM有多个访问源,那么显然应该定义一个仲裁和优先级形式。由于侦测控制单元需要最低时延(SCU既可以是处理器内核也可以是AXI ACP接口),因此SCU从这些访问源的读操作就具有最高优先级,紧接着是SCU写操作,然后是OCM互联读/写操作。用户可通过将片上存储器控制寄存器 中的SCU写操作的优先级设置为低来颠倒SCU写操作和OCM互联访问的优先级。

OCM本身结构为128位字,分成四个64KB分区,并位于PS地址空间的不同位置。初始配置下,前三个64KB区块布置在地址空间的起始位置,最后一个64KB区块置于地址空间的末尾(见图5)。

简单的片上存储器实例

您可使用赛灵思I/O函数访问OCM,以便从所选的存储器地址读取和写入数据。这些函数包含在Xil_IO.h中,可支持在CPU地址空间内存储和 访问8位、16位或32位字符型、短整型或整型数据。使用这些函数时,只需知道您希望访问的地址以及想要在此存储的值即可。如果是写操作,方法如下,

使用该技术时要确保两个地址指向片上存储器中的相同位置,尤其是当不同人编写不同内核程序时更应如此,为此更好的方法是使用共同的头文件。该文件将包含针对特定传输的相关操作地址的宏定义,例如:

另一种备选方法是让两个程序都使用指示器来访问存储单元。您可以通过使用宏命令定义指向恒定地址的指示器(一般用C语言)来实现这一点:

此外,您还可以对地址再次进行宏定义,以确保该地址为两个应用程序的共用地址。这种方法无需使用赛灵思I/O库,而是通过指示器实现简单访问。

处理器间的中断

Zynq SoC中的每个内核都有16个软件生成的中断。如上文所提到的,每个内核都能实现自身与另一个内核或两个内核的中断。使用软件中断与使用硬件中断基本相 似,区别只在于您如何触发它们。若使用软件中断,正在接收的应用就无需针对更新数据而对目标存储单元进行轮询。

就像使用任何硬件中断时一样,您需要对两个内核中的通用中断控制器进行配置。敬请参阅《赛灵思中国通讯》第87期的“如何在Zynq SoC上使用中断”以了解更多相关信息。

然后,您可以使用xscugic.h中提供的XScuGic_SoftwareIntr函数在正在更新的内核中触发软件中断。该命令将向该指定内核发出一个软件中断,再由该内核进行适当操作:

您必须为内核0和内核1应用对DDR存储器进行正确分段,否则会存在其中一个应用破坏另一个应用的风险。

创建应用

将文件添加到库之后,下个阶段就是生成AMP解决方案的三个重要部分:AMP第一阶段引导载入程序、内核0应用和内核1应用。您必须为每个部分生成一个不同的板支持包(BSP)。

您需要做的第一件事是用SDK创建一个新的FSBL。选择“新建应用项目”,创建一个支持AMP的FSBL项目。这与创建一般FSBL的过程没有什么不同。不过,这次您需要选择“Zynq FSBL for AMP”模板,如图3所示。

完成AMP FSBL创建之后,接下来需要为第一个内核创建应用。一定要选择内核0和您的首选操作系统,并允许其创建自己的BSP,如图4所示。

创建应用之后,您需要正确定义应用在DDR存储器中的位置(应用将从该位置执行)。为此,您需要编辑图5中的链接器脚本,以显示DDR的基地址和大 小。这一点很重要,因为如果没有为内核0和内核1应用对DDR存储器进行正确分段,就会存在其中一个应用破坏另一个应用的风险。

完成分段之后,您现在可以编写希望在内核0上执行的应用,因为该内核是AMP系统中的主管。内核0必须启动内核1应用的执行。您需要将图6中的代码 段包含在应用中。这段代码禁用片上存储器上的高速缓存,并将内核1程序的起始地址写到一个内核1将会访问的地址。一旦内核0执行Set Event(SEV)命令,内核1便开始执行其程序。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网