(摘抄和节选自最新一期的Xcell杂志)

By Paul Dillien and Tom Kean, PhD

保护信息的典型策略是当数据在网络中传递和在数据中心内流动的时候,对数据进行加密处理。万一数据被未经授权的嗅探链接拦截了,加密处理能保证数据不可读。理论上,数据也必须被授权来保证完整性。消息授权机制被设计来侦听原始加密数据在何处发生改变,不管这个改变是由传输错误导致,还是出于获得优势的目的而被黑客恶意篡改而导致。

以太网标准的流行推动了成本的下降,使其更有吸引力,这种良性循环也确保以太网继续成为选择中的2层技术。尽管如此,在一些年之前,规范中并没有关于加密的相关内容,以致把这项工作留给IPsec之类的技术来完成,而IPsec运行在通信协议栈的上层。

如今,新拓展的以太网标准增加了一系列符合IEEE 802.1AE规范的安全措施。在几年前这个技术获得认证,该技术具有一个集成的安全系统,可以加密和认证信息,同时也检测出并战胜了一系列的网络攻击。这个规范通常被称为媒体访问控制安全标准,简称MACsec,Algotronix公司几年前就开始生产能提供硬件加速的加密IP核,其拥有广泛的数据速率范围。(Algotronix公司也提供符合IPsec规范的知识产权核,该核拥有和MACsec标准产品相似的接口,可以很好满足系统支持双标准的需求。)

MACsec的理念源自于网络上的各个节点形成了一组可信实体。每一个节点可以接收密文和明文,系统协议决定前两者具体该如何处理。对于没有经过认证和确认的明文信息,MACsec核包含了一个旁路选项。IPsec之类的协议作用在3/4层,并且采用的是端到端的技术,MACsec协议则与之不同,其解析和确认数据包的时刻发生在数据包进入或离开以太网的时候。

数据包在数据中心进行传递时,数据中心选择2层连接可以达到拥有最小时延和最小包数据开销的高速传输。相比之下,如果在通信中使用如IPsec之类的3层技术,信息必须被传到堆栈等待处理,导致时延增大。2层技术的解决方案也可以消除建立3层安全协议时的复杂性。数据中心可以利用MACsec来提供防火墙背后的数据保护,或者把MACsec用到数据中心之间的直接链路中去。

对于MACsec,可定制的FPGA将是完美的解决方案,因为要适应不同市场需求。对于Algotronix公司,开发MACsec核是自然而然的事情,因为我们已经创造出了一系列被称为AES-GCM的加密引擎。这些核可工作在1G,10G和40G的不同频率下。我们通过流水线、提高时钟速度、逐步从如赛灵思Artix升级到Kintes再到Virtex FPGA等等方式来达到如此高的频率。目前我们正在采用这些技术来把Virtex UltraScale设备的吞吐量提高到100G的频率。

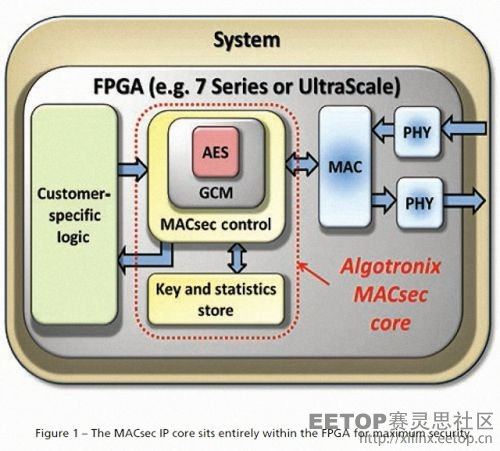

在FPGA中使用IP核可以达到不同层次的性能,其支持从任何地方由Gb以太网到10Gb以太网的传输(即理想最坏情况下核的实际吞吐速度),计划能有40G和100G版本。这比基于软件的系统所能达到的速度要快多了。如图1所示,这些核通常和硬件MAC直接互连,原因是FPGA芯片中嵌入式处理器里的软件很难以如此高的数据传输速率来处理数据吞吐量。如果安全功能被加载在硬件上,继而使得软件很难获得未加密的秘钥,那么系统就不会在常见的软件攻击如木马和病毒面前显得不堪一击了。

另外一个重要的考虑因素是,在使用FPGA进行算法加速的系统里,如加速由软件实现的加密功能,功耗节省这点非常重要。相比软件解决方案,FPGA省电效率更高。

这篇博客只是部分节选,想要在最新一期的Xcell杂志中阅读全文,点击这里。

© Copyright 2014 Xilinx Inc

如需转载,请注明出处