DDRSDRAM是建立在SDRAM的基础上的,但是速度和容量却有了提高。首先,它使用了更多的先进的同步电路。其次,它使用延时锁定回路提供一个数据滤波信号。当数据有效时,存储器控制器可使用这个数据滤波信号精确地定位数据,每16位输出一次,并且同步来自不同的双存储器模块的数据。

DDR SDRAM不需要提高时钟频率就能加倍提高SDRAM的速度,因为它允许在时钟脉冲的上升沿和下降沿读写数据。至于地址和控制信号,还是跟传统的SDRAM一样,在时钟的上升沿进行传输。

由于微处理器、DSP等不能直接使用DDR SDRAM,所以本文介绍一种基于FPGA的DDR SDRAM控制电路。

1 DDR SDRAM控制器的设计

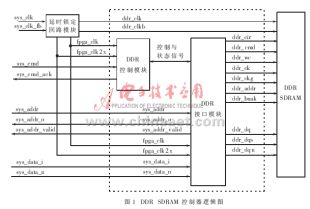

1.1总体逻辑图

DDR SDRAM控制器的总体逻辑图如图1所示。主要由DDR控制模块(Controller)、DDR接口模块(ddr_interface)以及延时锁定回路模块(DLL)三部分组成。下面详细介绍各个模块的设计。

1.2 DDR控制模块的设计

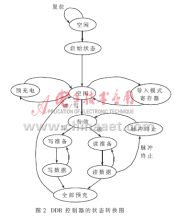

DDR控制模块包含了主要的状态转换。处理器通过sys_cmd对DDR控制模块写入命令,完成总线仲裁、解释命令、时序分配等任务。当DDR接口模块对DDR SDRAR数据读写时便进行控制。

控制器的状态机如图2所示。控制器开始设置在空闲(Idle)状态,接下去的状态根据控制命令的不同可以是预充电(Precharge)、导入模式寄存器(Load ModeRegister)、刷新(Refresh)、有效(Active)等状态。要进入读写数据状态,必须先经过有效状态。读数据时,状态机由有效状态转换为读准备状态, 然后根据指令进入读状态。控制模块保持在读状态直到脉冲终止命令触发或者数据读完。写的过程与读类似,在后面的接口模块中将详细介绍。

1.3 DDR接口模块

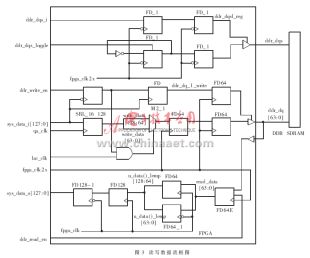

DDR接口模块负责维持外部信号、DDR控制器与DDR SDRAM之间的双向数据总线信号,保证数据和命令能送达DDR SDRAM。

图3给出了读写操作的数据流框图。对写周期而言,128位的sys_data_i被fpga_clk2x分频为64位的数据,通过lac_clk选择高低位。为了减小输入输出的延迟,数据在进出模块时都将被保存在输入输出寄存器中。ddr_write_en产生ddr_dq所需的三态信号。

对于写周期而言,64位的ddr_dq信号在输入输出寄存器被fpga_clk2x触发装配成128位的信号,其中低位信号在下降沿时被装配,高位信号在上升沿时被装配。

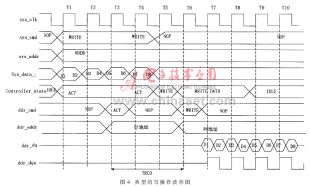

图4给出了一个典型的写操作的波形图。在T1期间,写命令、地址和第一个128位数据被分别置于sys_cmd、sys_addr和sys_data_i三个端口。在T2期间,控制器的状态由空闲转变为有效。接下来两个周期,控制器给出ACTIVE命令以及行片选地址。再经3个周期的延迟以后,控制器给出WRITEA命令和列片选地址。接下来,ddr_dq和ddr_dqs被设置成双倍速率模式。

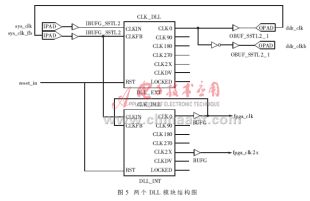

1.4 DLL模块

图5示出了给FPGA以及DDR SDRAM提供时钟信号的两个DLL模块的结构图。第一个DLL模块,即DLL_EXT给DDRSDRAM提供ddr_clk及ddr_clkb两个时钟信号,并且接收ddr_clk的反馈。第二个DLL模块,即DLL_INT给FPGA提供两个内部时钟信号fpga_clk和fpga_clk2x,它的反馈信号来自fpga_clk。两个DLL有着相同的时钟输入,但是不同的反馈信号保证了输入时钟和FPGA时钟以及DDR SDRAM时钟之间的零延迟。

2 实现

本设计选用XILINX公司的Vietex-E系列FPGA来实现,因为这个系列内嵌的DLL模块和可选择输入输出结构的特点能极大地方便设计。仿真结果显示,在133MHz的主频下,最高能获得1.6GB/s的速率。

本文给出了基于FPGA的DDR SDRAM控制器的设计。从仿真中可以看出,这种结构的DDR控制器有着很高的性能,因此将得到广泛的应用。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网