作者:Adam Taylor

研究了相关的时序约束后,在设计中我们也不能忽视所能运用到的物理约束。一个工程师最常用的物理约束是I/O管脚的放置和与每个I/O脚相关的参数定义(标准、驱动能力等)。然而,还有其它类型的物理约束:

• 放置约束——定义元件位置

• 布线约束——定义信号布线

• I/O脚约束——定义I/O脚位置和I/O脚参数

• 配置约束——定义配置方法

按照惯例,有一些约束独立于这些组之外。Vivado套件有三个约束,并且主要用于网表:

• DONT_TOUCH——用来防止优化。在实现严格安全和高度可靠系统方面有很大的作用。

• MARK_DEBUG——用来保留一个RTL以便将来调试使用

正如上面提到的,最常用的约束同I/O脚放置及其配置相关。这些设置选项在较大的系统和硬件中有很重要的影响。总而言之,它们是操作起来很敏感的地方。

在FPGA上,I/O的管脚放置同时使用了用来定位物理管脚位置的放置约束和来配置I/O口属性(例如I/O口标准、转换率等)的I/O口约束。现代FPGA可以支持一定数量的单端和差分I/O口标准。这些是通过I/O约束来定义的。然而,工程师必须小心确保它们遵循着I/O分组规则,这个取决于最后的管脚放置。

但什么是I/O分组规则呢?FPGA上的每一个用户I/O被组合在一起,形成有一定I/O脚数量的组。这些组有独立的电压供应,与组的层次相适应,支持宽范围的I/O标准。

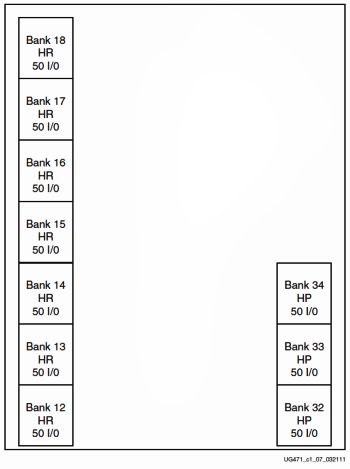

在Zynq Soc和其它赛灵思7系列设备上,I/O组被进一步地分类归属到两个整体组中的一个中去,从而进一步约束了它们的性能并且要求工程师使用正确分类的正确接口。第一个I/O组分类是高性能(HP),即被优化来获得更高的数据速率。高性能组类中的I/O脚使用较低的操作电压,并且不支持LVCMOS 3.3V和2.5V I/O电压级别。宽范围(HR)组分类被优化来支持高性能组所不支持的宽电压波动I/O标准。下面的插图显示了赛灵思Kintex XC7K325T FPGA上可用的HR和HP I/O组。

7系列FPGA XC7K325T中HR和HP I/O分组情况

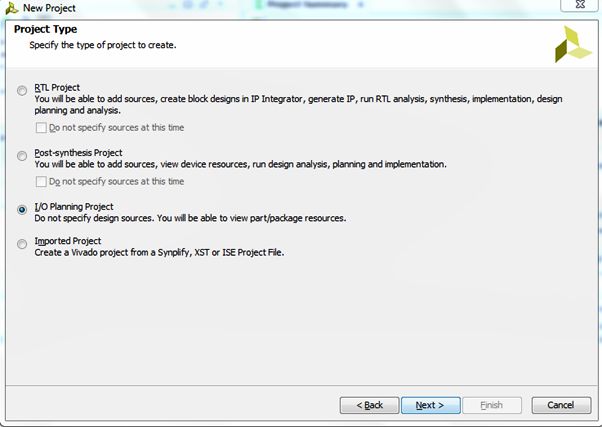

HP和HR组的I/O分组规则见用户指南471中的表1-55。在开发初期,很值得我们花费时间来理解这些规则。为了有助这个,Vivado套件提供创建I/O布局工程的可能:

一旦我们决定了在哪个信号中使用哪种I/O组后,我们仍然有能力来改变信号驱动能力和转换率。为了优化板子上的信号完整性,这些参数会对你的硬件设计团队有很大的吸引力。这些选项也将影响板子设计的时序。

信号完整性(SI)工具需要一个I/O管脚的IBIS模型,利用文件->导出->导出IBIS模型选项,当我们已经打开工程的时候,我们可以从Vivado套件中提取IBIS模型。这个导出文件可以用来关闭系统级别的SI问题和最终PCB布线的时序分析。

一旦设计团队总体上对SI性能和系统时序比较满意,我们将会以下面一些设计中用到的I/O约束来结束这部分:

• 设置属性管脚包装 G17 [获取端口{dout}]

• 设置属性 IO标准LVCOMS33 [获取端口{dout}]

• 设置属性转换率[获取端口{dout}]

• 设置属性驱动 4[获取端口{dout}]

我们也可以利用HP I/O组中可用的数字控制阻抗来适时地结束I/O,来增加系统的信号完整性,而不需要利用外部的结束计划。

我们也必须考虑没有信号来驱动I/O时的影响。例如,如果I/O脚和外部连接器相连,我们可以利用I/O约束来实现一个上拉或下拉电阻以保护FPGA输入信号免于悬空。悬空的输入可能导致持续和间歇的系统问题。

当然,通过用I/O块自身来实现最终的输出触发器,我们也能使用物理约束来改进设计时序。这样做减少了时钟输出时间。在输入信号上我们也可以做相同的工作,这样可使设计满足引脚到引脚所需建立和保持时间的要求。

在下一期博客中,我们将研究在FPGA逻辑设计中可以怎么利用放置和布线约束。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

©Copyright 2014 Xilinx Inc

如需转载,请注明出处