作者:Steve Leibson, 赛灵思战略营销与业务规划总监

Luis Bielich所撰写的名为“Zero Latency Multiplexing I/O for ASIC Emulation”的Xilinx应用手册XAPP1217介绍了一种技术。这种技术使用一个高速的串行接口,将许多并行数据位从一个FPGA移动到另一个FPGA。可以实现零延迟传输,也就是将多个数据位从一个FPGA瞬移到另一个FPGA。当然,这里所谓的零延迟,要求FPGA的系统时钟显著的慢于串行数据的波特率。这点对ASIC一般是试用的,同时他也可适用于其他的很多应用场合。例如在不同的板卡之间的数据传输,两个FPGA的距离稍微远一点。Bielich的技术可以用最小数量的I / O引脚实现多bit数据的传输,比如一个引脚。

多路复用多位超高速链路的概念非常简单,从应用手册截取了下图1,如图所示:

想要从这项技术中得到“零延迟”,必须要求串行端口波特率必须显著高于逻辑时钟频率。

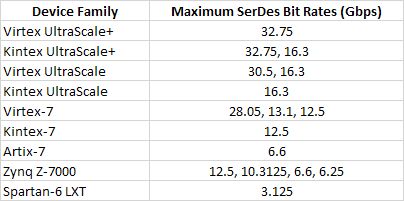

赛灵思7系列、UltraScale、UltraScale+以及Spartan-6所有的可编程器件的串行端口比特率是相当高的。以下是为Xilinx产品SerDes端口的最大比特率(单位为Gbps)的表格:

图2:Xilinx所有可编程设备系列最大的SerDes端口速度

显然,当你拥有UltraScale和UltraScale+设备的SerDes端口极端比特率时,这种位隐形传输技术会运用得非常好,但很多人会发现使用速度较慢的SerDes端口,该技术同样适用。这一切都取决于你需要实现多快的位隐形传输。就比如,不是每个人都需要零延迟,但减少了I / O引脚的数量始终是方便的。

本应用手册展示了如何计算运输率以及如何计算在一个给定的系统时钟周期内你能传输的潜在有效位的个数。它还展示了如何通过使用Vivado设计包来实现这种技术。同时还有其他一些相关的技巧。

Click here to get Application Note XAPP1217, “Zero Latency Multiplexing I/O for ASIC Emulation”

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/I-O-bit-teleportation-using...

©Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网