所有的Virtex UltraScale中和部分的Kintex UltraScale器件中已经加入了150G Interlaken总线协议

作者:Steve Leibson, 赛灵思战略营销与业务规划总监

随着FPGA越来越大,许多系统开始逐渐整合到一个可编程器件里面了。

但并不是所有。

由于各种各样的原因,一些大型系统仍然要用多个器件来实现,这些器件间采用高效快速的芯片与芯片间互联对于提升系统级性能有重要的意义。随着多Gbps级SerDes端口的崛起,在过去的十年里可扩展的Interlaken总线协议已经成为实际上的芯片与芯片之间互联的标准,尤其在网络领域。在前几代的赛灵思的FPGA中就支持使用 Interlaken 协议的软核。所有的Virtex UltraScale器件和一些Kintex UltraScale器件包含了多个已嵌入150Gbps Interlaken总线协议的硬IP核,这些IP核可以使您更加方便的使用高效、快速的标准化的芯片与芯片之间协议互联。

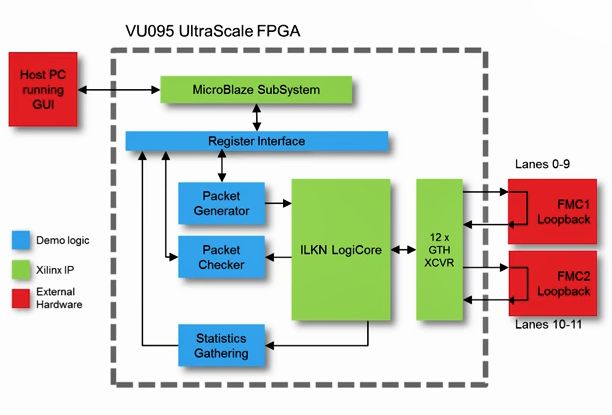

下面4分钟的视频为您提供了关于UltraScale体系架构这方面的简要概述。演示视频展示了在VCU107 Eval开发板上的Virtex UltraScale VU095全可编程器件在12.5Gbps速度下运行12 个Interlaken总线通道,仅用12对差分对就能达到150Gbps 总峰带宽。以下是该系统演示框图:

Virtex UltraScale VU095 FPGA上拥有6个片上、低延迟Interlaken内核,在视频演示中仅仅用了一个。下面就是这个视频:

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Need-a-high-speed-chip-to-c...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处