RLOC约束的定义使用到了表达式 RLOC=XmYm,此处X和Y指的是FPGA阵列中的坐标。定义一个RLOC时,我们既可以使用相对坐标,也可以使用绝对坐标,取决于RPM_GRID属性值,这个值决定了该定义是绝对的还是相对的。

由于这些约束是用HDL定义的,为了正确地定义布线,在约束被添加到HDL文件中之前,很有必要对布局走线迭代进行初始化。

和很多东西一样,这些概念最好能用例子来阐述。下面这个例子中包含两个切换的寄存器。其中一个寄存器长度为2位,用来同步输入。第二个切换寄存器长16位。它使输出信号延时16个时钟。为了展示上面的约束,我将把一个绝对RPM应用到长为2位的同步器中,然后把相对RPM应用到16位寄存器中。

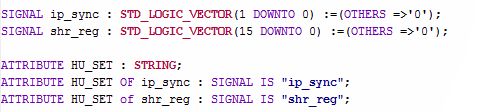

第一件要做的事情就是利用RTL声明U_SET或者HU_SET约束组。由于这是个推断的信号,因此我们需要定义x_SET而不是SIGNAL和LABLE参数。

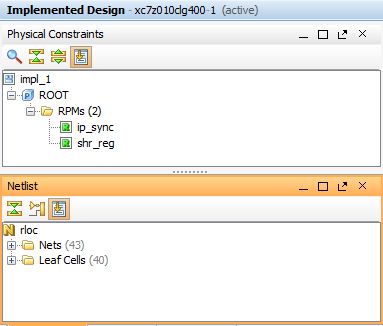

当我们打开implementation并实现了上面这些的时候,我们可以在物理约束窗口下看到RPM。

在U_SET和HU_SET约束定义好了后,下一步就是定义RPM的位置了。然而,在干这件事情之前,最好知道RPM中元件的数量。通过点击目标RMP,选择RPM属性,我们可以获取RMP中元件的数量。

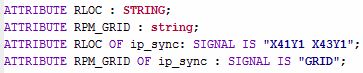

接下来,我们将要在规划好的地方不相干地放置输入寄存器。利用下面显示的RPM_GRID属性,我们完成这一步:

这个操作将会在由一个片分开的片上放置两个ip_sync信号寄存器。尽管对于日常设计来说这并不是一个好的尝试,但是它展示了此处我们所讨论的RPM原则。

约束将会导致切换寄存器中的寄存器彼此相关地放置。为了做到这一点,我们不使用网格约束,取而代之,我们按照下面这种方式使它们彼此靠近地放置。

对于每个寄存器的16位元素,当我们在设备视图中查看布局的时候,我们将得到上述约束增量与原点的距离图作为结果。

中间列的垂直触发器代表切换寄存器,而旁边两列上的两个寄存器是ip_sync寄存器,被定义跳过一个slice。

从这里你可以下载源码例程。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/Adam-Taylor-s-MicroZed-Chro...

©Copyright 2014 Xilinx Inc

如需转载,请注明出处