作者:Steve Leibson, 赛灵思战略营销与业务规划总监

老式的VMEbus其根源可以追溯到32bit的VERSAbus,由1970年代摩托罗拉半导体产品集团的Jack Kister针对68000微处理器而设计的。VME是 Versa Module Europe的缩写,它放弃了VERSAbus的板边插接器为了更加可靠的DIN连接。首个32位VME板开始出现在1980年代早期,到1994年,VMEbus已经演变成VME64,在VMEbus制造商集团的赞助下,它成为一个非常成功的开放式总线规范,现在被称为VITA。VMEbus的长寿和VITA的努力维护和升级了VME标准作为先进的电子技术导致在过去的几十年里有大量的VME板被设计。

很快进到21世纪,你会发现,选择使用PCIe总线的非常多,主要是其在PC领域获得巨大的成功。IOxOS技术(电子设计公司,主要针对航空、物理、和电信行业)现在提供了一个十分成熟的 PCIe-to-VME桥 IP模块作为 一个预编译的,加密的二进制配置文件准备移入Xilinx Artix-7 FPGA。

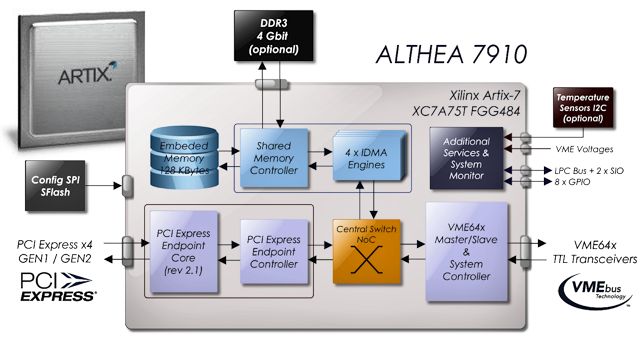

IOxOS技术的ALTHEA 7910 PCI Express到 VME64x 桥IP核从2009年开始就已经在所有公司的VME SBC(单板计算机)成功的实现了和验证了,并已用于许多处理器包括英特尔x86(Xeon、i5 / i7),AMD(皓龙处理器)和PowerPC(QorIQ P和T系列)等平台上运行微软的Windows XP和Windows 7,Linux,以及Wind River的VxWorks。这个IP核为你提供了低延迟,高带宽桥到 一个PCIe上游端口,带VME64x主/从接口,Slot-1功能和中断管理。这里有一个ALTHEA 7910核的框图。

你也许不需要一个PCIe-to-VMEbus64桥,但是IOxOS技术的ALTHEA 7910 PCI Express到 VME64x 桥 IP核,展示了一个解决更大问题的方案,那就是桥接过去到现在和未来。FPGA擅长桥接,因为他们快速、灵活、有很多的I / O端口。为了桥接功能你需要这三个必不可少的因素。

仔细看看上图IOxOS 技术的 ALTHEA 7910模块框图。除了相对简单的桥接,有额外的功能包括四方DMA引擎,DDR3 SDRAM控制器,电源和温度监测。这些功能提高性能,改善系统的可靠性,通常需要至少能够方便旧的设计适应现在的需求。IOxOS核适合在一个Artix-7 XC7A75T FPGA,它是7系列Artix-7低端FPGA一个中型的成员。因为它是基于一个高端的、低功耗的台积电(TSMC)28 nm HPL IC工艺,Xilinx Artix-7全可编程设备可以实现桥接功能与低功耗的要求。 IOxOS技术的ALTHEEA 7910 IP核在Artix-7 XC7A75T FPGA内消耗的电少于1.5W。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/IP-bridges-VMEbus-to-PCIe-p...

© Copyright 2014 Xilinx Inc

如需转载,请注明出处

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网