作者:Carol A. Fields

赛灵思公司

选择合适的千兆位收发器(GT)是通信和实时处理领域尤其需要重点考虑的设计事项,但特定的市场领域可能会存在太多的标准、协议或使用模型。有时针对某一种应用就会涉及到好几种标准,为了选择最适合的千兆位收发器,必须对各种协议的最新发展情况了如指掌。

从无线通信到消费电子产品的众多不同市场领域都具有业界标准连接协议。了解高级协议及其与低层协议规范的关系并充分留意不同行业对PHY定义的情况,将有助于选择最好的LogiCORE IP高速串行收发器架构向导协议模板,进而实现我们的设计目标。首先来回顾一下这些相关协议。

OSI:连接协议模板

开放系统互连(OSI)是一种面向全球通信的ISO标准。该标准定义了一个分七层实施协议的框架。控制信息从某一站点的应用层开始向下逐层传递,直至最底层的物理层,随后通过通道传输到下一站点。而信息返回时经过各层的顺序则与之相反。

三个PHY子层

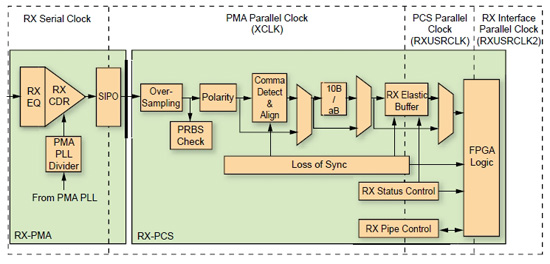

当前普遍使用的许多串行连接协议都在模仿OSI的分层模型。PHY层包括2??3个子层,分别为物理编码子层(PCS)、物理介质连接(PMA)子层和可选的物理介质相关子层(PMD)。图1以方框图的形式显示了各层之间的关系。

Virtex-5 RX物理子层PCS、PMA和PMD示例方框图

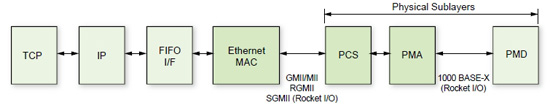

数据包或数据在发送时以正向顺序传输,即从介质访问控制(MAC)层到PCS、PMA及PMD,而接收时的顺序则与之相反。

PHY使用方面的混乱状态

人们很容易将PHY误认为是硅芯片,而混淆其用途。PHY是一个包括子层的规范层。我们可用单一或多个器件实施设计人员通常称之为电子规范的PHY.对子层的使用主要取决于具体的细分市场和所用协议。

通信协议中的PHY层通常使用的是PCS、PMA和PMD子层。图2显示的是在局域网应用中使用赛灵思TEMAC (10M/100M/1G) LogiCORE的示例,其中千兆位以太网MAC接连与1000BASE-X PCS/PMA和激光收发器1000BASE-X PMD进行通信。此时,PHY同时实施在了FPGA和可选的光学收发器器件之中。

以太网通信应用中的PHY PCS、PMA和PMD层示例

赛灵思通常会在FPGA中直接集成PCI Express和千兆位以太网等常用的协议。这硬化版本可实施协议的部分或全部功能。在上述这两种情况中,LogiCORE封装作为LogiCORE产品的一部分实施MAC和物理层(PCS和PMA)。封装包含硬化模块并与高速串行收发器相连接。就TEMAC而言,硬化IP实施MAC和部分PCS以及 PCI Express LogiCORE的事务处理和数据链路层。可用赛灵思的高速串行收发器向导来查看并修改GTP/GTX设置。

10Gb以太网——XAUI

10Gb以太网标准是一种IEEE规范,其定义的标称速率是千兆位以太网的10倍。物理层包含的一个接口可将MAC连接于PHY、PCS、PMA和 PMD.至于赛灵思LogiCORE,10Gb媒体独立接口(XGMII)可连接至光学模块或10Gb以太网XAUI.PMA和PMD既可视为外部器件(如在光学收发器中),也可以视为XAUI的一部分(如在芯片间或背板应用中)。

通用分组无线接口v4.0

通用分组无线接口(CPRI)可用于无线电设备控制器或基站以及一个或多个无线电设备单元之间的连接。CPRI规范涵盖了OSI堆栈的第一层和第二层,物理层(第一层)定义了传统基站使用的电气接口以及支持远程无线电设备的基站光学接口。赛灵思CPRI LogiCORE在GT中实施PHY,在FPGA逻辑中实施数据链接(第二层)。

3G和6G OBSAI RP3-01

OBSAI RP3-01蜂窝式基站协议分为较低的物理层和较高的应用、传输和数据链路层。应用层可连接于基带或RF卡,而数据链路层可连接于物理层。赛灵思用FPGA中的收发器实施PHY,处理电气部分,并连接到外部光学收发器模块。

第一代和第二代PCI Express

PCI Express协议应用于物理层、数据链路层和事务处理层。由于这种标准非常通用,因此新兴串行协议往往寻求在电气规范方面与其兼容或类似,据此,ASSP和其他PHY器件厂商就能重用精心测试的IP产品了。赛灵思通过自身及其AllianceCORE合作伙伴在集成式硬IP模块和软IP中实施了第一代和第二代PCI Express协议。

串行RapidIO

虽然串行RapidIO协议与PCI Express一样也应用于三个层中,但却分别为物理层、逻辑层和传输层。由于RapidIO和XAUI的应用目标类似,串行RapidIO设计人员因而能重用其现有的XAUI电气设计方案。赛灵思GT向导可通过串行RapidIO模板支持串行RapidIO PHY.

三速SDI视频

三速SDI视频参考设计是基于SMPTE标准之上的。与高速串行收发器的物理连接是通过差动CML驱动外部线缆驱动器(用于传输)或外部适应性接收均衡器来实现的。各标准间常用的串行化协议非常具体,设计时采用的是FPGA结构。该协议需要较多的AC耦合电容进行大量的1和0运算。

赛灵思三模以太网

三模以太网MAC是赛灵思实施10/100/1Gb以太网协议的一种标准。赛灵思提供TEMAC LogiCORE(软IP)和用于集成模块的三模以太网封装(硬IP)。就软IP而言,1000BASE-X PCS/PMA或SGMII LogiCORE可实现无缝连接。SGMII是支持10/100/1G操作的串行连接标准。

TEMAC封装即硬TEMAC子块和GT I/O块中通常采用的HDL封装(1000BASE-X/SGMII已经集成于TEMAC)。具体实施细节请查阅以太网LogiCORE文档资料。

GT向导支持采用GigE (SGMII/1000Base-X)模板的三模以太网协议。

总而言之,业界标准协议日新月异,差不多每年都会出现一两种新标准。因此就这点而言,其术语和基础技术的复杂程度堪比税法。而对给定协议的物理层方案了解得越详细,就越易于确定所要使用的极佳高速串行收发器向导协议,从而为设计项目开创一个良好的局面。

本视频基于Xilinx公司的Artix-7FPGA器件以及各种丰富的入门和进阶外设,提供了一些典型的工程实例,帮助读者从FPGA基础知识、逻辑设计概念

本课程为“从零开始大战FPGA”系列课程的基础篇。课程通俗易懂、逻辑性强、示例丰富,课程中尤其强调在设计过程中对“时序”和“逻辑”的把控,以及硬件描述语言与硬件电路相对应的“

课程中首先会给大家讲解在企业中一般数字电路从算法到流片这整个过程中会涉及到哪些流程,都分别使用什么工具,以及其中每个流程都分别做了

@2003-2020 中国电子顶级开发网